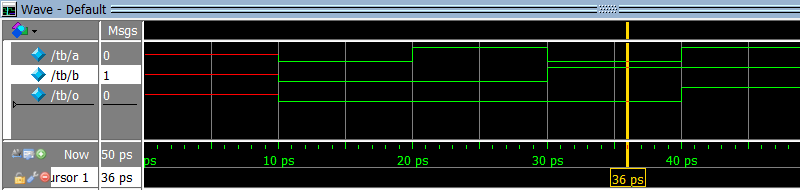

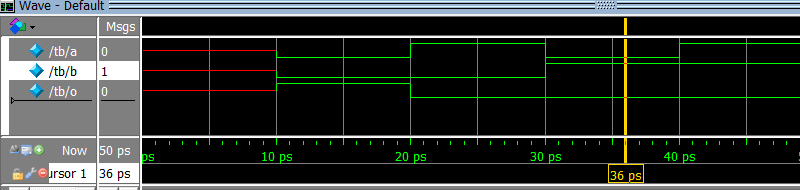

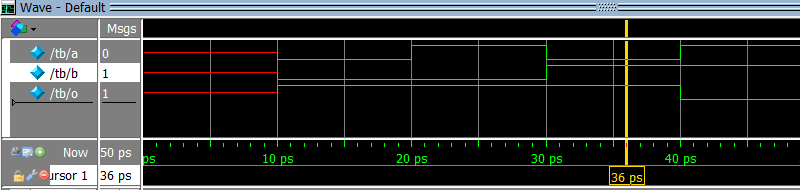

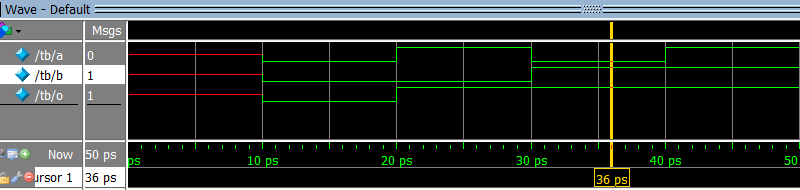

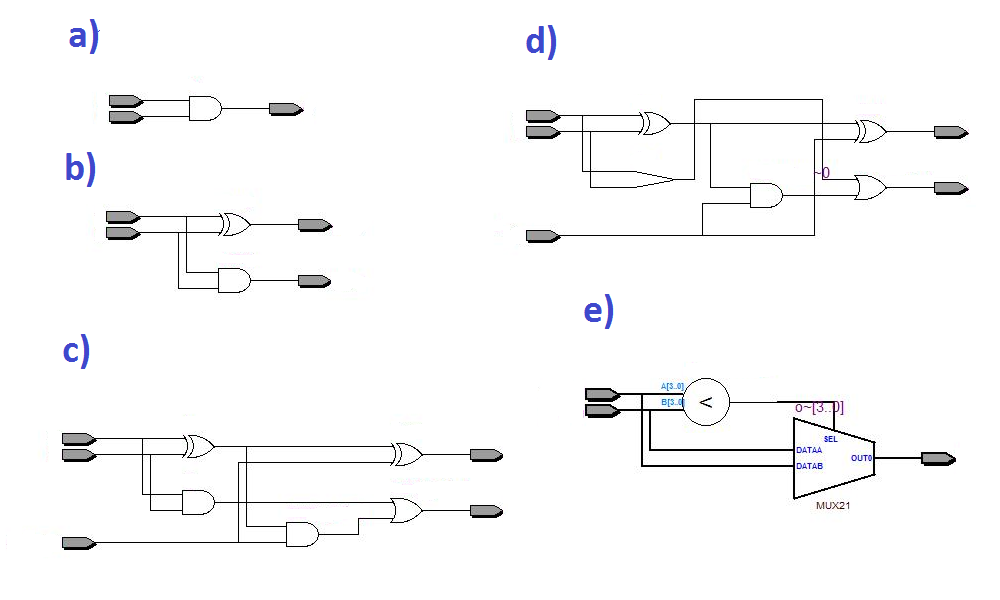

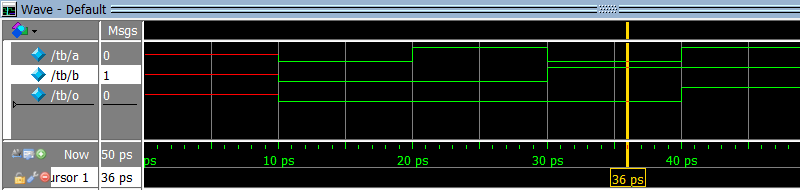

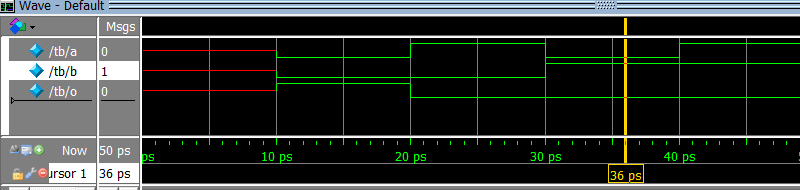

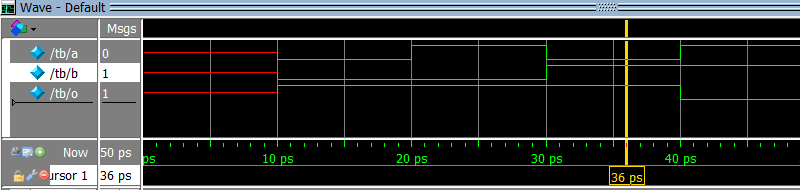

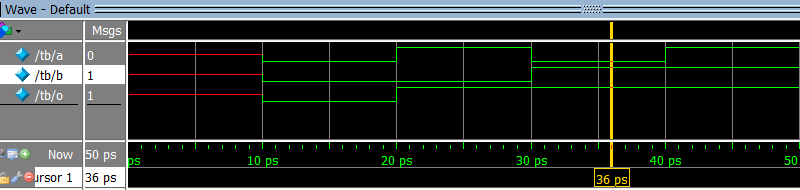

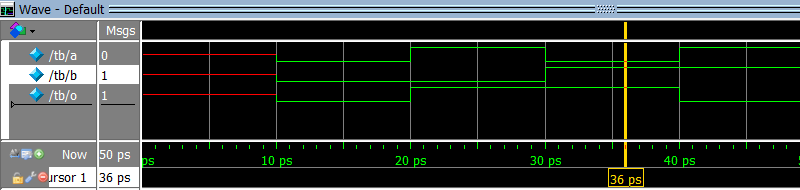

1. Which waveform is the result of the simulation below?

module design (input a, input b, output o);

assign o = a & b;

endmodule

module tb;

logic a, b, o;

design design_inst (a, b, o);

initial

begin

$dumpvars;

$monitor ("%t a %b b %b o %b", $time, a, b, o);

#10;

a = 0; b = 0; #10;

a = 1; b = 0; #10;

a = 0; b = 1; #10;

a = 1; b = 1; #10;

end

endmodule

a)

b)

b)

c)

c)

d)

d)

e)

e)

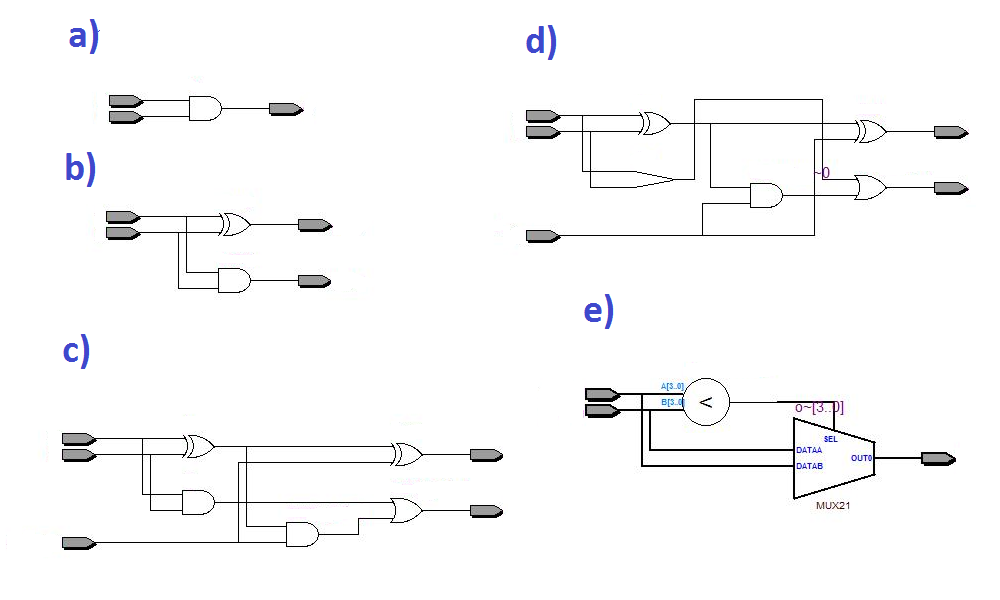

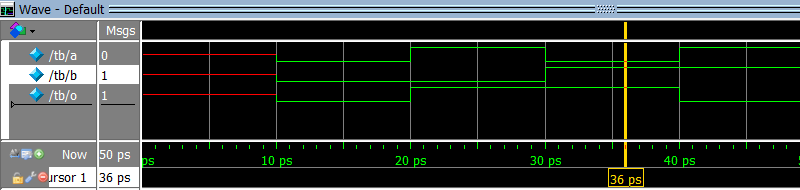

2. What is the result of synthesis of this module?

module design

(

input a,

input b,

input carry_in,

output sum,

output carry_out

);

wire p = a ^ b;

wire q = a & b;

assign sum = p ^ carry_in;

assign carry_out = q | (p & carry_in);

endmodule

2. What is the result of synthesis of this module?

module design

(

input a,

input b,

input carry_in,

output sum,

output carry_out

);

wire p = a ^ b;

wire q = a & b;

assign sum = p ^ carry_in;

assign carry_out = q | (p & carry_in);

endmodule

b)

b)

c)

c)

d)

d)

e)

e)

2. What is the result of synthesis of this module?

module design

(

input a,

input b,

input carry_in,

output sum,

output carry_out

);

wire p = a ^ b;

wire q = a & b;

assign sum = p ^ carry_in;

assign carry_out = q | (p & carry_in);

endmodule

2. What is the result of synthesis of this module?

module design

(

input a,

input b,

input carry_in,

output sum,

output carry_out

);

wire p = a ^ b;

wire q = a & b;

assign sum = p ^ carry_in;

assign carry_out = q | (p & carry_in);

endmodule