For Distribution

Сравнения MIPS и ARM для случая MIPSfpga / MIPS microAptiv UP

## Преимущество MIPS M14K против ARM Cortex-M3

#### Согласно независимому аналитическому журналу

#### MICROMIPS CRAMS CODE

New Processor Cores Introduce Denser 16/32-Bit Instruction Set

By Tom R. Halfhill {11/16/09-01}

Smaller is usually better for embedded processors, so MIPS Technologies is slimming down its 1980s-vintage instruction-set architecture. A new set of 16- and 32-bit instructions—dubbed microMIPS—uses less memory than existing 32-bit MIPS instructions and the

16-bit extensions added in the 1990s.

MicroMIPS will debut early next year in two new embedded-processor cores, the MIPS32 M14K: The M14K is an improvement on the MIPS32 M34K processor, introduced in 2002. It's a relatively simple, cacheless core intended for 32-bit microcontrollers in automobiles, industrial machinery, consumer electronics, and office equipment.

In bigger bottom, the Marke, sign minuses and the bigger bottom, and the bigger bottom of the MARC, as an introduced in 2000. The MARC has an MAU with a translation lookacide buffer (TIAB), making it suitable for sophisticated embedded operating systems that manage virtual memory. It's designed for advanced consumer electronics, including DTVs. DVD players, set-top boxes, home networking equipment, personal enter-timment devices and digital cameras. Figure 1 shows how the M14K and M14Ke fit into the MIPS product line.

Both new processors respond much faster to interrupts and have better debugging features than the MIPS cores they supersede. Both gain advantages in clock speed, power consumption, and core size when compared with ARM's Cortex-M3 and ARM'926 processors, and they give ARM's new Cortex-A3 are to for the most give ARM's new Cortex-A5 are to for the most prive ARM's new Cortex-A5 are to for the most and they give ARM's new Cortex-A5 are to for the most final factors.

advantages in clock speed, power consumption, and core size when compared with ARM's Cortex-M3 and ARM'826 processors, and the give ARM's new Cortex-A5 are in for the money.

NOVEMBER 16, 2009 MICROPROCESSOR REPORT

#### MIPS Fares Well Against ARM

Perhaps the most surprising result of comparing the new MIPS processors with ARM's best cores is that ARM no longer has a clear advantage in power consumption, core area, and performance. Usually, those are ARM's strengths.

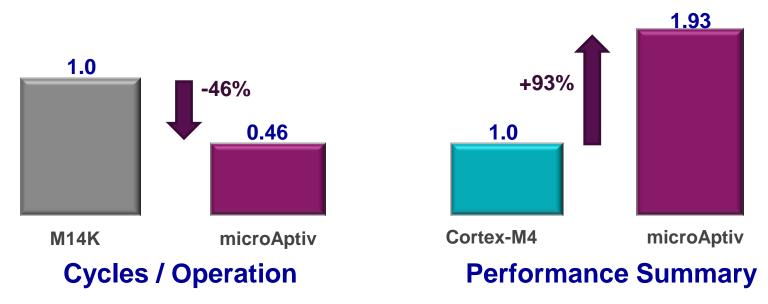

For instance, using the data in Tables 2 and 3, we can compare the two microcontroller cores—the MIPS M14K and ARM Cortex-M3—in the same TSMC 90nm-G process. An area-optimized M14K will consume 11.6mW at 193MHz in 0.21mm² of silicon. A speed-optimized Cortex-M3 will consume 13.3mW at 191MHz in 0.37mm² of silicon. The M14K requires less power and silicon at virtually the same clock frequency. In power efficiency, the M14K wins, too: 25Dmips per milliwatt versus 17.9Dmips per milliwatt.

Note that we compared an area-optimized M14K with a speed-optimized Cortex-M3. That's because a speed-optimized M14K can reach a much higher clock frequency (295MHz). Assuming the two processors are clocked to deliver similar performance, the M14K will use less power and silicon. (The M14K has a throughput advantage of 1.5Dmips per megahertz versus 1.25Dmips per megahertz for the Cortex-M3.)

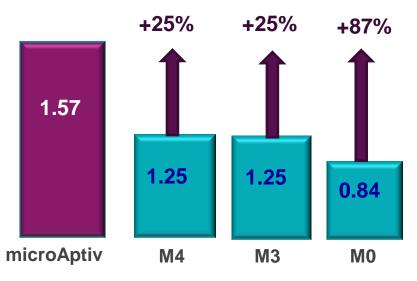

### **Better Performance vs ARM Cortex M Series**

**Dhrystone – DMIPS/MHz**

- ❖ microAptiv outperforms Cortex M Series by up to 87%

- **❖** Lower clock speed needed to achieve equivalent performance

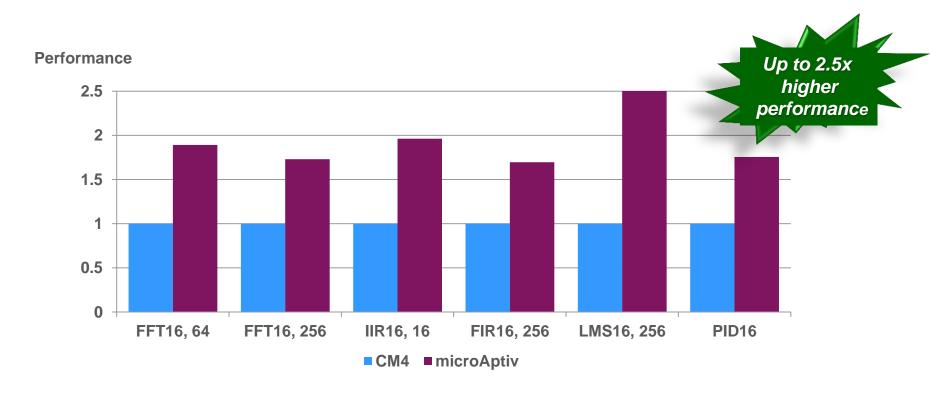

### Better DSP Performance vs ARM Cortex M4

Running MIPS DSP Libs and ARM CMSIS DSP: FFT, FIR, IIR, LMS, PID, VMUL, H.264

microAptiv outperforms Cortex M4 by >90% for DSP operations

# microAptiv vs. Cortex-M4 DSP Performance

Comparing DSP performance (higher is better) executing microAptiv DSP Library and Cortex M4 CMSIS Library

## microAptiv vs Cortex-M Series Feature Comparison

**Reduces Code Size With No Loss in Performance**

Best Performance Efficiency

Better Real Time Performance

**Faster Code Execution**

**More Flexible**

|                                    |                         | -                   |                        |

|------------------------------------|-------------------------|---------------------|------------------------|

| FEATURE                            | microAptiv UC           | Cortex-M3           | Cortex-M0              |

| Architecture                       | Harvard                 | Harvard             | Von Neumann            |

| Pipeline stages                    | 5                       | 3                   | 3                      |

| ISA                                | MIPS32 and/or microMIPS | Thumb-2             | Thumb/Thumb-2 (subset) |

| Legacy 32-bit decoder              | Y - MIPS32 optional     | N                   | N                      |

| Total instructions                 | 300+                    | 155                 | 56                     |

| DMIPS Performance                  | 1.57 DMIPS/MHz          | 1.25 DMIPS/MHz      | 0.9 DMIPS/MHz          |

| Performance/Area Efficiency (90LP) | 40 CM/MHz/mm2           | 27 CM/MHz/mm2       | 28 CM/MHz/mm2          |

| GPRs                               | 32                      | 16                  | 13                     |

| GPR sets (max)                     | 16                      | 1                   | 1                      |

| Interrupt control                  | Y - int & ext           | Y - int NVIC        | 32                     |

| Priority levels                    | 8                       | 4                   | 4                      |

| Interrupt latency                  | 10 cycles               | 12 cycles           | 16 cycles              |

| Tailchaining                       | Υ                       | Υ                   | Υ                      |

| MMU                                | Y - FMT                 | N                   | N                      |

| MPU (optional)                     | Y - up to 16 regions    | Y - up to 8 regions | N                      |

| Multiply-Divide unit               | Y                       | Y                   | Multiply only          |

| Atomic bit instructions            | Υ                       | Y                   | N                      |

| Instruction-only trace             | Υ                       | N                   | N                      |

| PC sampling                        | Υ                       | N                   | N                      |

| Perfomance counter                 | Υ                       | N                   | N                      |

| Fast Debug Channel                 | Υ                       | N                   | N                      |

| 2-wire Debug                       | Y                       | Y                   | Y                      |

| Secure Debug                       | Υ                       | N                   | N                      |

| Local Code Ram (max)               | 4GB                     | 1GB                 | None                   |

| Local Data Ram (max)               | 4GB                     | 1GB                 | None                   |

| Parity                             | Optional                | N                   | N                      |

| Fast SRAM interface                | Υ                       | N                   | N                      |

| Flash memory prefetch              | Υ                       | N                   | N                      |

| External interface                 | AHB-Lite                | AHB-Lite            | AHB-Lite               |

| Co-Processor interface             | Υ                       | N                   | N                      |

| Custom Instruction support         | Υ                       | N                   | N                      |

## microAptiv vs Cortex M4 Feature Comparison

| FEATURE                         | microAptiv              | Cortex M4 |

|---------------------------------|-------------------------|-----------|

| Core                            | M14K                    | Cortex-M3 |

| Cache version                   | Υ                       | N         |

| Pipeline Stages                 | 5                       | 3         |

| ISA                             | MIPS32 and/or microMIPS | Thumb2    |

| Total instructions              | 300                     | 155       |

| DMIPS Performance (DMIPS/MHz)   | 1.57                    | 1.25      |

| Performance Efficiency (CM/mm2) | 2200                    | 2000      |

| GPRs                            | 32                      | 16        |

| GPR sets (max)                  | 16                      | 1         |

| Closely coupled memory support  | Υ                       | N         |

| MPU Support                     | Υ                       | Υ         |

| MMU support                     | Υ                       | N         |

| Interrupt latency               | 10 cycles               | 12 cycles |

| Tailchaining                    | Υ                       | Υ         |

| Instruction-only trace          | Υ                       | N         |

| PC sampling                     | Υ                       | N         |

| Perfomance counter              | Υ                       | N         |

| Fast Debug Channel              | Υ                       | N         |

| Single wire debug               | 2-wire cJTAG            | Υ         |

| FPU option                      | N                       | Y         |

## microAptiv vs Cortex M4 Feature Comparison

| DSP FEATURE                     | microAptiv      | Cortex-M4       |

|---------------------------------|-----------------|-----------------|

| DSP Instructions                | 159             | 80              |

| SIMD - 8/16                     | Y               | Y               |

| SIMD Instructions               | 70              | 38              |

| Integer & Fractional data types | Υ               | Y               |

| Saturate, Rounding options      | Υ               | Υ               |

| Dedicated DSP/MDU unit          | Υ               | N               |

| Accumulators                    | Y (4)           | N               |

| Multiply/MAC instructions       | 38              | 29              |

| 32x32, 16x16, dual 16x16        | Υ               | Υ               |

| 16x8                            | Υ               | N               |

| dual 8x8                        | Υ               | N               |

| 32x16                           | N               | Υ               |

| Single cycle instructions       | Υ               | Υ               |

| Shift Instructions              | Υ               | N               |

| Bit Manipulation                | Υ               | Υ               |

| Compare/Pick                    | Υ               | N               |

| Data Pack/Unpack                | Y               | Y               |

| Bit Reversed Addressing         | Y (instruction) | Y (instruction) |

| Modulo addressing               | Y (instruction) | N               |

For Distribution

Спасибо!