# **Teaching Materials**

# Introduction

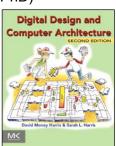

MIPSfpga provides the RTL source code of the MIPS microAptiv UP core for implementation on an FPGA, together with teaching materials. The MIPS microAptiv UP core is a member of the same microcontroller family found in many embedded devices, including the popular PIC32MZ microcontroller from Microchip and Samsung's new Artik1.

The teaching materials will show you how to use this core as part of a Computer Architecture course, paving the way for your students to explore how a commercial pipelined processor core works inside and to use this core in their projects, in effect creating their own SoC designs.

With its long heritage and excellent documentation, MIPS is the preferred choice of RISC architecture for many teachers around the world. But in the past, to demonstrate key concepts, teachers had to settle for creating partial 'MIPS-like' cores or using unofficial copies of dubious heritage. Not now! MIPSfpga is the real 'industrial' RTL, non-obfuscated, and available freely for academic use.

# **Structure**

The MIPSfpga teaching materials consist of three parts:

- The **Getting Started Package** contains a detailed guide that begins with a brief introduction to the MIPSfpga core included in the package. It gives a brief overview of how to setup the core for simulation or putting it on to an FPGA, as well as programming the processor. Guides on software installation are also given, along with detailed references about the core and its ISA Instruction Set Architecture. All users need this package first.

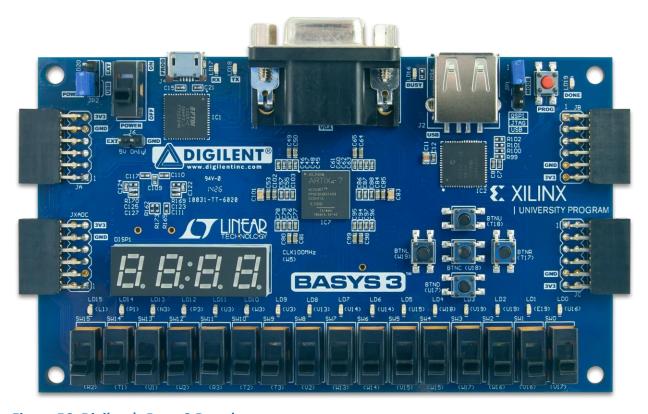

- MIPSfpga **Fundamentals**. In here you will find slides with accompanying lab scripts, illustrated using the Nexys 4 DDR and DE2-115 platforms. With this you will be taken from building the core, to programming in both c and assembly, with exercises to complete along the way. You then move on to adding a range of peripherals to the core to enable a greater level of interaction. The final example takes you through porting MIPSfpga to other FPGA boards such as Basys 3.

- MIPSfpga **SOC**. The Advanced package enables you to run Buildroot Linux on MIPSfpga specifically using the Nexys4 DDR platform. The microAptiv core is packaged as an IP block usable by Vivado IP Integrator. As a result, AXI based IP blocks from Xilinx can easily be interfaced with the MIPS core. These are used to create an example SoC, such as a design with a UART and Ethernet, running under Linux, on MIPSfpga. A custom AXI GPIO block along with an example Linux driver is also provided. There is extensive documentation included. Collectively these provide an excellent basis for a SoC course that is highly relevant to the needs of the chip design industry, although the

level of complexity makes this a postgrad class. PhD students and Postdocs will also find this material very useful for advanced projects.

# **Target Courses & Projects (Education Level)**

- Digital Design & Microarchitectures (BSc)

- Computer Architecture, Advanced Computer Architecture (BSc, MSc)

- SoC design (MSc)

- Design Verification (MSc)

- Embedded Systems projects (BSc, MSc)

- Processor Architecture: modifications, enhancements, optimisation...(MSc, PhD)

# The Authors

The course materials were developed by David Harris and Sarah Harris, coauthors of the popular textbook Digital Design and Computer Architecture which provides a uniquely relevant accompaniment to MIPSfpga.

# **Complementary Materials**

The textbook 'Computer Organisation and Design' by David Patterson and John L. Hennessy remains the 'bible' for these activities, and provides further depth to Harris & Harris in a MIPSfpga-based course.

http://community.imgtec.com/university/resources/books/?subject=mips-architecture

Access the microAptiv core in silicon through boards such as Digilent's 'WiFire' incorporating Microchip's PIC32MZ MCU.

Videos of the workshop given by Sarah Harris and Parimal Patel of Xilinx will be posted online in September 2015 here: http://community.imgtec.com/university/video-gallery/

# **Required Tools**

### Hardware

- Host PC: Windows 64 bit

- Digilent Basys 3 or Nexys 4 DDR, with Xilinx Artix FPGA

- Porting to other boards has been shown: Zed board, Nexys 3, Nexys 4 (not DDR), DE0-CV and SP605

- JTAG Probe: SEEED Studio MIPS Bus Blaster including 14 to 6 pin adaptor (for Digilent boards)

### **Software**

• Codescape MIPS SDK Essentials (included with Getting Started Package)

- Vivado (Xilinx) Web Pack edition

- Open OCD (included with Getting Started Package)

- Mentor Graphics ModelSim (Student or Full editions) or Xilinx Xsim

# **Core Structure**

The core is approximately 40K gates.

# **Languages available for Getting Started & Fundamentals**

- English

- Simplified Chinese

- Japanese

- Russian

- Spanish

# Support

- The MIPS insider forum here has a thread specifically for technical questions about MIPSfpga

- For curriculum and other discussions, there is the IUP (Imagination University Programme) forum here

# **Partners**

We have worked closely with Xilinx and Digilent who have given wonderful support to this large and complex project.

Details on their University Programmes are here: http://www.xilinx.com/support/university.html https://learn.digilentinc.com/list

# **User Licenses**

• For the MIPS core:

The agreement is part of the Getting Started Package download process, and acceptance is required before the download request can be submitted. The End User Licence Agreement (EULA) allows the use of the MIPS core on FPGA platforms for the academic purposes of teaching, student projects and research. It allows teachers to distribute the core to students in classes, and it allows for the core to be modified. It does not allow the core to be put into silicon. Furthermore, if the core is modified and the user wishes to patent these modifications, the licence requires that this is negotiated with Imagination first.

The EULA is written in plain English, and a copy of the EULA is part of the Getting Started package for future reference.

• For the **Teaching Materials**:

The agreement is part of the Fundamentals and Advanced download process. The End User Licence Agreement (EULA) explains that the materials are for Educational and Non-Commercial use, which means that companies or trainers who wish to use the materials for paid-for training, must seek Imagination's prior permission. Distribution of the materials to your Students is expressly allowed. The agreement allows extracts of the material to be used in derived teaching materials as long as Imagination's copyright is acknowledged, but publication in textbooks needs prior permission (which is usually given). No warranty is provided as to the effectiveness of the materials. The EULA is written in plain English, and a copy of the EULA is included in the materials package for future reference.

# **Plans**

We are always pleased to hear about your needs for Teaching Materials. Our focus over the next year will be on workshops to promote use of MIPSfpga, releasing the Advanced package, debugging the existing materials, and listening to your feedback through the MIPSfpga thread on the forums. In addition, we are working on an 'MPW' route for researchers who would like to implement MIPS in silicon.

What we do after that will be determined primarily by you!

# **Press Release & Blogs**

Free and Open Access to a Modern MIPS CPU

http://imgtec.com/news/press-release/imagination-revolutionizes-cpu-architecture-education-with-free-and-open-access-to-a-modern-mips-cpu-3/

MIPSfpga programme opens up the MIPS architecture to universities worldwide http://blog.imgtec.com/mips-processors/mipsfpga-opens-up-the-mips-architecture-to-universities-worldwide

# How to join the IUP and access these materials

- 1. Click 'Register' or 'Join IUP' on the landing page: www.imgtec.com/university

- 2. Complete the first section: 'the Community Registration'

- 3. Tick the box marked 'Join Imagination University Programme' and completes the additional information

- A verification email will be sent to your inbox for activation.

(Please also check your spam mailbox because occasionally the mail will got filtered)

- 5. To download teaching materials, visit the IUP page -Resources http://community.imgtec.com/university/resources/

- 6. Request the package(s) you want, accept the Licence Agreement, and give some details about how you plan to use the materials.

- 7. We then receive a request to approve the download, and normally action this within 48 hours. Once approved, you will receive an e-mail saying you can now make the download.

NOTE: Requests may be rejected for the following reasons

- The registration details are incomplete

- There are few or no details of intended use

- The requester appears to be a commercial company or a competitor

Please feel free circulate this information to anyone who might be interested and keep an eye on our webpages for further information such as workshops and updated packages.

# Lab 1

# **Setting up a Vivado Project for MIPSfpga**

These materials produced in association with Imagination.

Join our University community for more resources.

community.imgtec.com/university

# MIPSfpga Lab 1: Setting up a Vivado Project

# 1. Introduction

This is the first in a series of laboratory exercises acquainting you with system-on-chip design using Imagination's MIPSfpga platform. In this lab you will learn to set up a Vivado project for simulating, synthesizing, and downloading the MIPSfpga system onto Digilent's Nexys4 DDR FPGA board. As you make changes to the MIPSfpga system in the future, you can follow these steps to compile, simulate, synthesize, download, and test your changes.

The instructions in this lab use Vivado 2015.1. Instructions for later versions of Vivado are similar, if not exactly the same.

# 2. Setting up a Vivado Project

In this section we walk through the steps of (1) creating a project for the MIPSfpga system, (2) simulating the project, (3) compiling the project, and (4) downloading the MIPSfpga system onto the Nexys4 DDR board.

Before setting up the Vivado project, make a copy of the MIPSfpga system by copying the **rtl\_up** folder in the MIPSfpga directory (provided with the MIPSfpga Getting Started materials) to **MIPSfpga\_Fundamentals\rtl\_up**.

The Verilog files in the MIPSfpga\_Fundamentals\rtl\_up directory describe the MIPSfpga system and are the design source files for the Vivado project you are about to create. In later MIPSfpga Fundamentals labs, you will extend the functionality of the MIPSfpga system by both modifying and adding Verilog files to the MIPSfpga\_Fundamentals\rtl\_up folder.

### Step 1. Create Vivado project

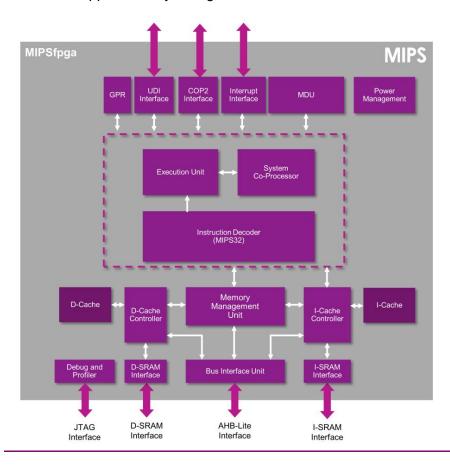

Start Vivado. Open a new project by choosing File > New Project (see Figure 1).

Figure 1. Create new Vivado project

Click **Next**. Browse to the MIPSfpga\_Fundamentals\Xilinx\LabO1\_Vivado folder and place the new project, **Project1**, in that folder, as shown in Figure 2. Click the Create Project subdirectory box and click next, as shown below.

Figure 2. Create Vivado project directory

In the next window, leave RTL Project selected and click Next.

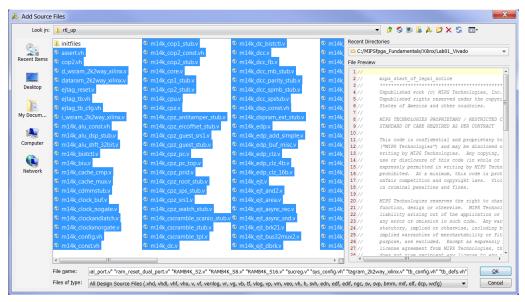

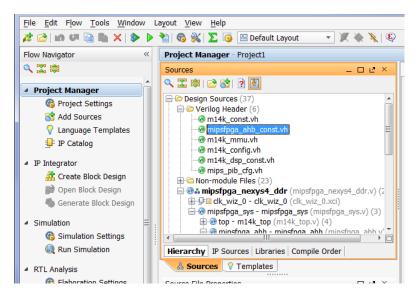

Now in the **Add Sources** window, click on the green plus sign and **Add Files**... Browse to the **MIPSfpga\_Fundamentals\rtl\_up** directory. Select all of the files (ctrl-a or click, shift-click), as shown in Figure 3, and click **OK**.

Figure 3. Adding Verilog files to project

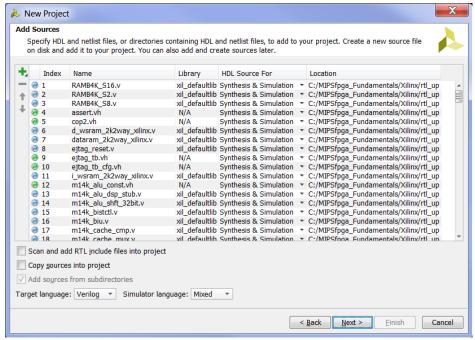

The project should refer to the Verilog (.v) and Verilog header (.vh) files located in the MIPSfpga\_Fundamentals\rtl\_up directory – you do **not** want to make a local copy of the files in

the Vivado project. So, in the next window, make sure the Copy the sources into Project box is **not** selected (see Figure 4) and click **Next**.

Figure 4. Adding Sources – do not copy sources into project

You will not add any IP, so click Next in the Add Existing IP (optional) window.

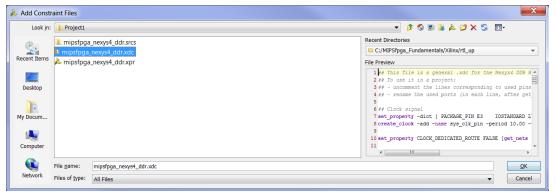

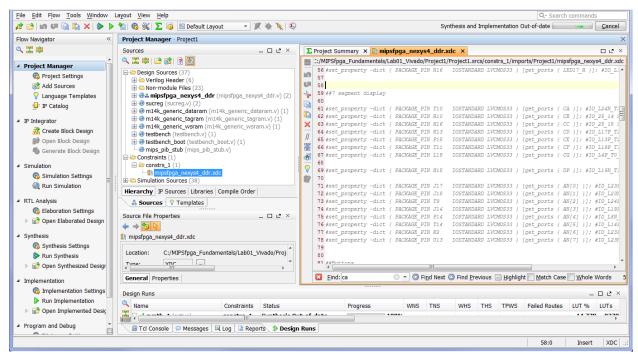

In the Add Constraints (optional) window, click on and Add Files... Browse to the MIPSfpga\_Fundamentals\Xilinx\Lab01\_Vivado directory. Select mipsfpga\_nexys4\_ddr.xdc and click OK (see Figure 5). This constraints file maps the Verilog signals to pins on the FPGA and describes timing constraints.

Figure 5. Add Xilinx Design Constraints (.xdc) file to Vivado project

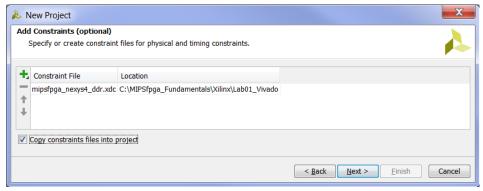

Click on the Copy constraints files into project box (see Figure 6) and click Next.

Figure 6. Copy .xdc file into Vivado project

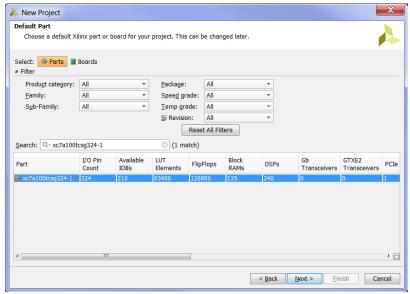

Now you will choose the Artix-7 FPGA that is on the Nexys4 DDR board as the target. Type (or copy-paste) the following into the search box: **xc7a100tcsg324-1**, as shown in Figure 7. Select the part, as shown, and click **Next**.

Figure 7. Selecting the Artix-7 FPGA

"xc7a" indicates that it is an Artix-7 FPGA. "100t" says that it has about 100k Logic Cells. "csg324" indicates a "chip scale ball grid array (BGA)" package with 324 pins, and "-1" is the speed grade.

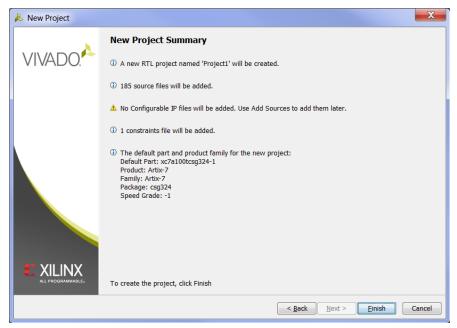

Now click **Finish** in the New Project Summary window (see Figure 8).

Figure 8. New Project Summary window

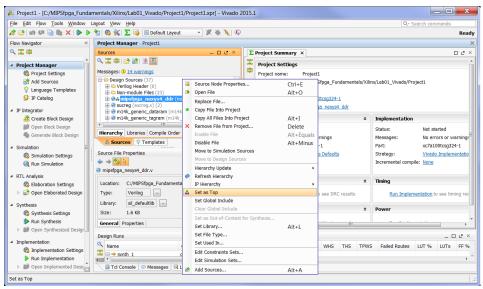

After the project initializes, go to the Project Manager window, right-click on mipsfpga\_nexys4\_ddr, and select **Set as Top** in the pull-down menu, as shown in Figure 9. This will set that module as the top-level module to synthesize, compile, and download to the Nexys4 DDR board.

Figure 9. Setting the top-level module for synthesis, implementation, and bitstream generation

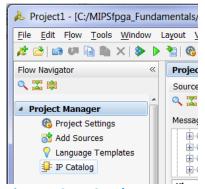

The last step of creating the project is to add a PLL that reduces the on-board 100 MHz clock to 50 MHz to meet timing constraints. To create the PLL, click on **IP Catalog** under Project Manager in the Flow Navigator, as shown in Figure 10.

Figure 10. IP Catalog

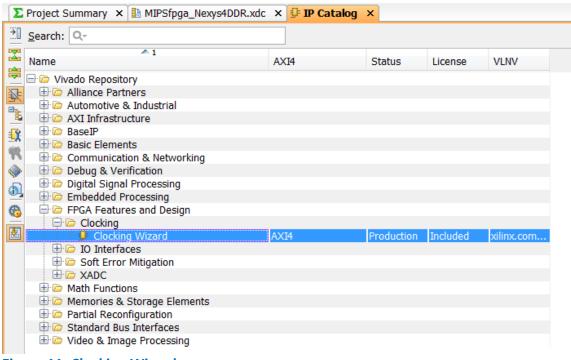

Now, in the IP Catalog tab of the Project Manager pane, expand **FPGA Features and Design**, and then expand **Clocking**. Double-click on **Clocking Wizard**, as shown in Figure 11.

Figure 11. Clocking Wizard

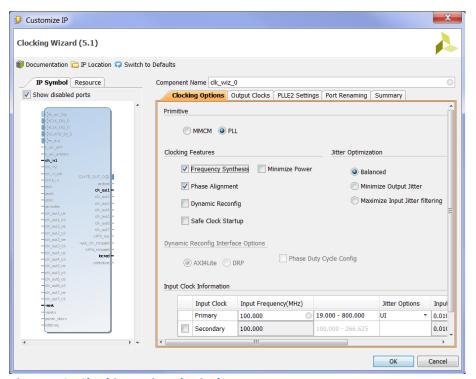

The Clocking Wizard window will pop up, as shown in Figure 12. Select **PLL**, as shown in Figure 12. Leave the Input Clock information as the default (100 MHz).

Figure 12. Clocking Wizard window

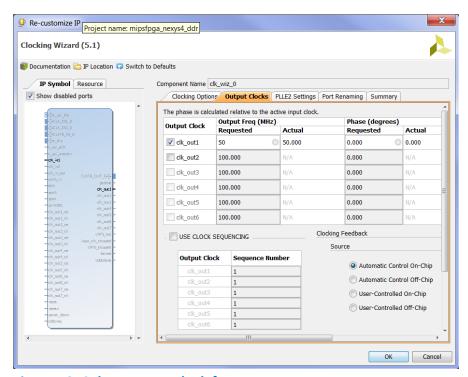

Now click on the **Output Clocks** tab, and type in **50** as the output frequency in the Output Freq (MHz) Requested box for clk\_out1, as shown in Figure 13.

Figure 13. Select output clock frequency

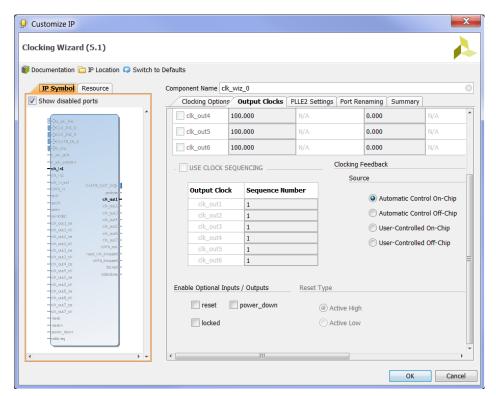

**Scroll down** in the same tab (Output Clocks) and **deselect** reset and locked, as shown in Figure 14. Then click **OK** to complete the creation of the PLL.

Figure 14. Deselect reset and locked

A pop-up window will prompt you to "Generate Output Products", as shown in Figure 15. Click **Generate**.

Figure 15. Generate PLL

A window will pop up that says "Out-of-context module run was launched for generating output products," as shown in Figure 16. Click **OK**.

Figure 16. Out-of-context generation of PLL

# Step 2. Simulating MIPSfpga

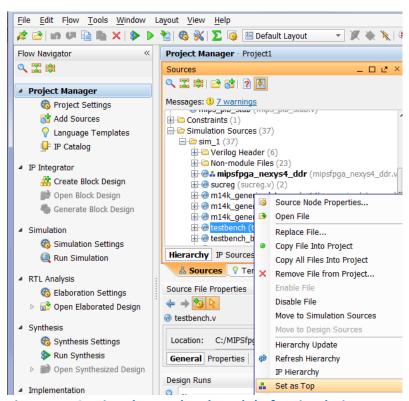

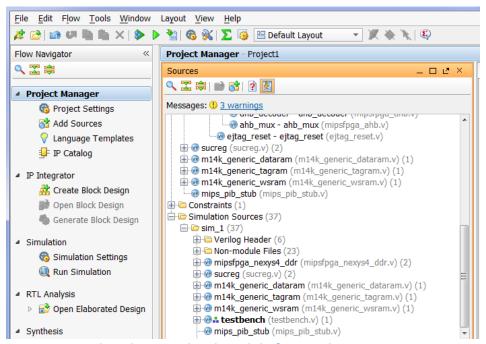

Now you are ready to simulate the MIPSfpga system. You will use Vivado's built-in simulator called XSIM. We already added the testbench.v file when we created the project, and now we will make it the top-level module for simulation. In the Project Manager panel, scroll down to **Simulation Sources** and expand it and the **sim\_1** folder.

Figure 17. Setting the top-level module for simulation

Right-click on testbench.v and **set it as the top-level module** for simulation, as shown in Figure 17. Notice that the testbench entry is now bold.

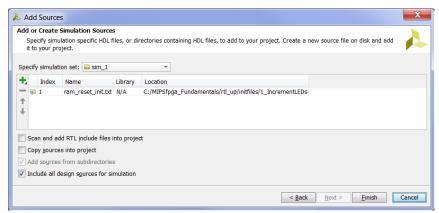

Click on **Add Sources** in the Flow Navigator window on the left, select **Add or create simulation sources** option, and then click **Next**. Click on and **Add Files...**, select **All Files** in the *Files of type* filter, browse to the ram\_reset\_init.txt file in

MIPSfpga\_Fundamentals\rtl\_up\initfiles\1\_IncrementLEDs, select it, and click **OK**. Leave the

Copy sources into project box unselected, but leave the Include all design sources for

simulation box checked, as shown in Figure 18. Then click **Finish**.

Figure 18. Adding simulation source

The text file contains the instructions that will be loaded into MIPSfpga's memory. As you recall from the MIPSfpga Getting Started Guide, this program, as shown in Figure 19 for your convenience, writes incremented values to memory address 0xbf800000. Also recall from the MIPSfpga Getting Started Guide that the LEDs on the Nexys4 DDR board are mapped to memory address 0xbf800000. So the program writes incremented values to the LEDs.

```

// C code

# MIPS assembly code

unsigned int val = 1;

\# $9 = val, $8 = mem address 0xbf800000

volatile unsigned int* dest;

addiu $9, $0, 1 # val = 1

dest = 0xbf800000;

$8, 0xbf80 # $8=0xbf800000

while (1) {

$9, 0($8) \# mem[0xbf800000] = val

L1: sw

*dest = val;

addiu $9, $9, 1 # val = val+1

beqz $0, L1

val = val + 1;

# branch to L1

# branch delay slot

nop

```

Figure 19. IncrementLEDs program

The equivalent machine code for the IncrementLEDs program is given in Figure 20.

| Machine Code | Instruction Address | Assembly Code     |                                |

|--------------|---------------------|-------------------|--------------------------------|

| 24090001     | // bfc00000:        | addiu \$9, \$0, 1 | # val = 1                      |

| 3c08bf80     | // bfc00004:        | lui \$8, 0xbf80   | # \$8=0xbf800000               |

| ad090000     | // bfc00008: L1:    | sw \$9, 0(\$8)    | # mem[0xbf800000] = val        |

| 25290001     | // bfc0000c:        | addiu \$9, \$9, 1 | # val = val+1                  |

| 1000fffd     | // bfc00010:        | beqz \$0, L1      | # branch to L1                 |

| 0000000      | // bfc00014:        | nop               | <pre># branch delay slot</pre> |

Figure 20. MIPS machine code

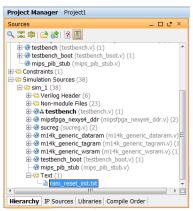

Expand the hierarchy under *Simulation Sources* and observe that ram\_reset\_init.txt is added in a separate sub-folder called Text and it contains the machine code (see Figure 21). Now you are ready to run the simulation of the MIPSfpga system running that program.

Figure 21. Text file as simulation source

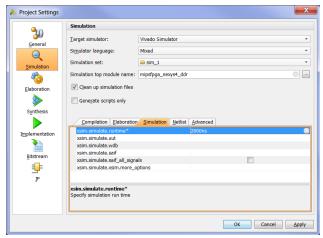

Click on **Simulation Settings** in the Flow Navigator window on the left, as shown in Figure 22.

**Figure 22. Simulation Settings**

The simulation settings window will show up, as shown in Figure 23. Make sure the Generate scripts only is **not** selected. Click on the Simulation tab and set **the simulation run time** to **2000 ns**. Click **OK**.

Figure 23. Change simulation run time

Click on **Run Simulation** → **Run behavioral simulation** in the Flow Navigator window, as shown in Figure 24.

Figure 24. Run simulation

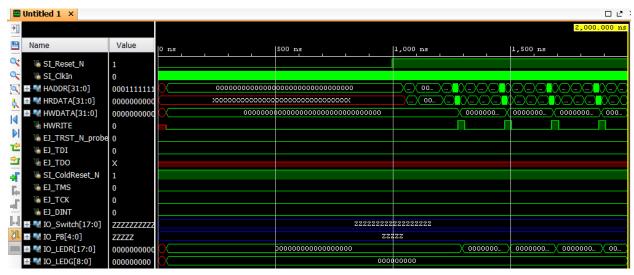

The testbench and lower-level modules will compile, the simulation window will open, and the simulation results will be displayed, as shown in Figure 25. You will see the top-level signals being displayed. Click on the Zoom Fit button ().

Figure 25. Simulation results showing top-level signals

Select all of the signals in the waveform window and then right-click and select **Radix → Hexadecimal**. Use shift-click and ctrl-click to select multiple signals at a time.

Delete all of the EJTAG signals and some of the I/O signals: EJ\_TRST\_N\_probe, EJ\_TDI, EJ\_TDO, SI\_ColdReset\_N, EJ\_TMS, EJ\_TCK, EJ\_DINT, IO\_Switch, IO\_PB, and IO\_LEDG. Do **not** delete IO\_LEDR. Right-click on a signal (or group of signals) and select Delete. (Or simply select the signals and press the Delete key.) Again, you can also select multiple signals using shift-click and ctrl-click.

The waveform window will now resemble Figure 26.

Figure 26. Keeping only the desired top-level signals

You can float the waveform window by clicking on the float button ( ) and then maximize it by clicking on the full size button (left one ). Click on the Zoom Fit button to see the waveform completely. You can also use Zoom In ( ), Zoom Out ( ), and Zoom to Cursor ( ) buttons to view a desired section of the waveform.

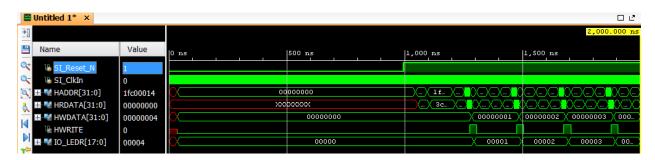

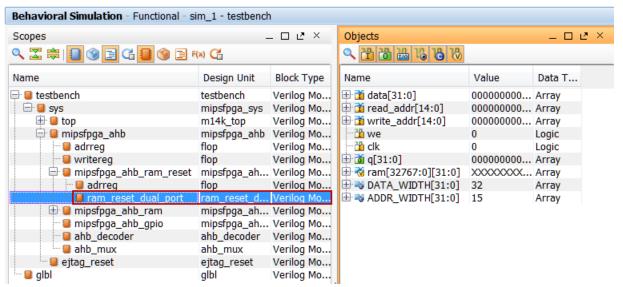

You can view signals from lower-level modules by adding them to the waveform. For example, as shown in Figure 27, expand the **testbench** hierarchy to **testbench**  $\rightarrow$  **sys**  $\rightarrow$  **mipsfpga\_ahb**  $\rightarrow$  **mipsfpga\_ahb\_ram\_reset** to see the **ram\_reset\_dual\_port** entry in the **Scopes** window. Click on the **ram reset\_dual\_port** entry to see the corresponding signals in the **Objects** window.

Figure 27. Accessing the signals of lower-level modules

In the waveform window, right-click in the signals area below the last signal, and select **New Divider**. The New Divider dialog box will appear. Type **Reset RAM Memory** in the field and press **Return**.

Select all of the objects in the **Objects** window, right-click and select **Add to Wave Window** and observe that the signals are added to the Waveform window. You can change the radix of the added signals to Hexadecimal as before. In the tool buttons bar, change the run time to 4 us

Now click on the Restart button and then click on the Run for

time> button to reset and run the simulation for 4 us. You will see the output as shown in Figure 28.

Figure 28. Simulation result showing lower-level module signals

At first the processor is reset: the low-asserted reset signal SI\_Reset\_N is low. Just after reset (when SI\_Reset\_N transitions from 0 to 1), you can view the waveform as it fetches each

instruction starting with instruction address 0x1fc00000. This address shows up on HADDR and the instruction read from memory appears on the HRDATA bus one cycle later. Recall that virtual address 0xbfc00000 translates to physical address 0x1fc00000. The instructions are executed in sequence until the branch is taken at 0xbfc00010. The code then continuously repeats from 0xbfc00008 – 0xbfc00014. Recall from the MIPSfpga Getting Started Guide, that until the caches are initialized by the boot code, each instruction takes 5 cycles. Also view how incremented values are written on the HWDATA signal as the code executes. HWDATA is the data being written to memory or, in this case, memory-mapped I/O. IO\_LEDR displays the incremented value because it is memory-mapped to address 0xbf800000. The IO\_LEDR signals are connected to the pins that drive the Nexys4 DDR's LEDs.

After you are finished viewing the waveform, you can close the simulator by selecting **File > Close Simuation**. A pop-up window will appear asking if you want to save the waveform. You could select Save but for now, click **Discard**.

# Step 3. Compiling MIPSfpga

Now you are ready to compile the MIPSfpga system and create a bitfile that you can download onto the Artix-7 FPGA on the Nexys4 DDR board. Click on the **Generate Bitstream** button at the top of the window. The bitstream is a file that configures the FPGA to be the MIPSfpga system, as defined by the Verilog files. This file is also referred to as the *bitfile*.

A window may pop up saying:

There are no implementation results available. OK to launch synthesis and implementation?...

Click **Yes**. Now wait for synthesis, placement, routing, and bitstream generation to complete. This typically takes around 10-20 minutes, depending on your computer speed.

After the bitstream has been generated, you will see the Bitstream Generation Completed popup window, as shown in Figure 29.

Figure 29. Bitstream Generation Completed pop-up window

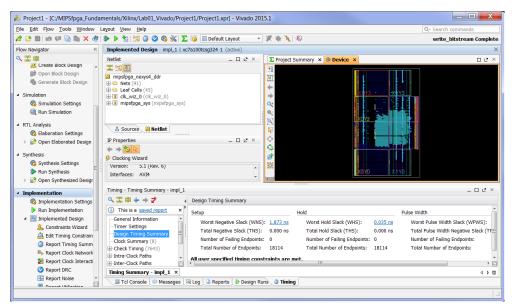

Viewing the implemented design is optional, but gives some insight into the timing and layout of the MIPSfpga core. (If you don't want to view it, select Open Hardware Manager and click OK. Then continue with Step 4 below.) To view the implemented design, leave **Open Implemented Design** selected, and click **OK**. This will take a few minutes. Then the Implemented Design window will open, as shown in Figure 30.

Figure 30. Implemented Design

Notice the **Design Timing Summary** pane at the bottom. Most importantly, it says that **All user specified timing constraints are met**. The Worst Negative Slack (**WNS**) is 1.273 ns and the Worst Hold Slack (**WHS**) is 0.052 ns, so there are no timing violations. The slack values for your project are likely slightly different. Each time Vivado places and routes the design, a different configuration results.

As you add to or modify the MIPSfpga system in the future, check that the timing constraints are met, and if not, reduce the frequency of the PLL and/or change the timing constraints in the Xilinx Design Constraints (.xdc) file until they are. The WNS will indicate how much the cycle time needs to be increased.

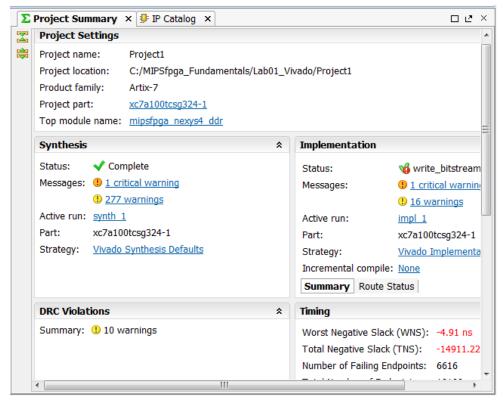

For example, Figure 31 shows a Project Summary page for a design that does **not** meet timing. Notice the negative values of WNS (shown in red). In this case the cycle time is too short by 4.91 ns, so add that amount (or slightly more) to the cycle time to meet timing. If the frequency of the failing design were 100 MHz (cycle time = 1/100 MHz = 10 ns), the cycle time would need to increase to at least (10 + 4.91) ns  $\approx 15$  ns (frequency = 1/15 ns  $\approx 66$  MHz).

Figure 31. Design that does not meeting timing constraints

## Step 4. Downloading MIPSfpga onto Nexys4 DDR FPGA Board

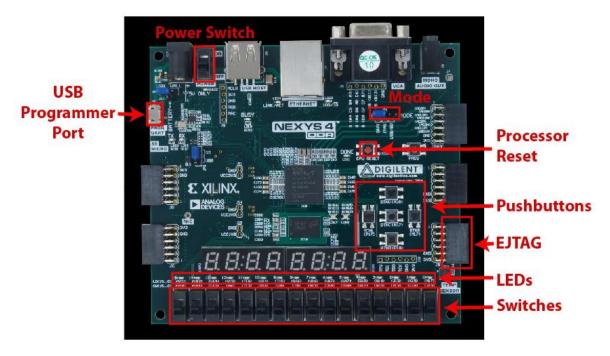

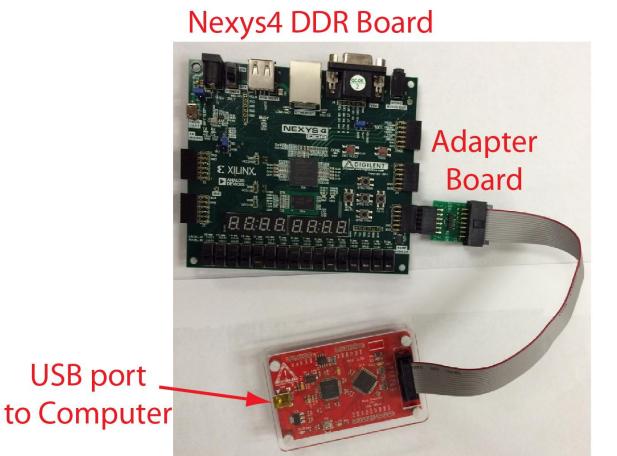

Now you are ready to download the compiled design onto the Nexys4 DDR FPGA board. First, connect and turn on the Nexys4 DDR board. Figure 32 shows the board and highlights the power switch and the USB port. Plug the standard end of the programming cable into your computer and the micro-USB end of the programming cable into the board, at the location labeled "USB Programmer Port" in Figure 32. Now turn the board's power switch ON. If the board is factory configured, the board will run a pre-loaded program that writes to the 7-segment displays with a snake-like pattern that repeats indefinitely. To program the board, it can be in QSPI mode (as shown in Figure 32 with the left-most Mode pins connected by a jumper) or in JTAG mode (with the two middle pins of the Mode selector connected by a jumper).

Figure 32. Nexys4 DDR board (photograph © Digilent Inc., 2015)

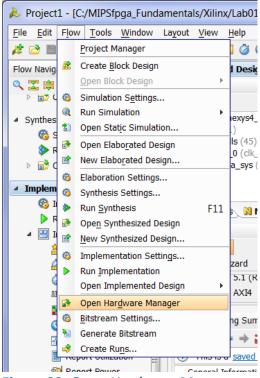

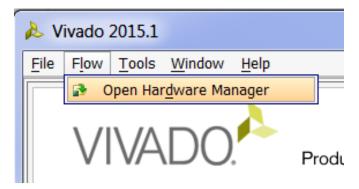

In the Vivado window, select **Flow \rightarrow Open Hardware Manager**, as shown in Figure 33.

Figure 33. Open Hardware Manager

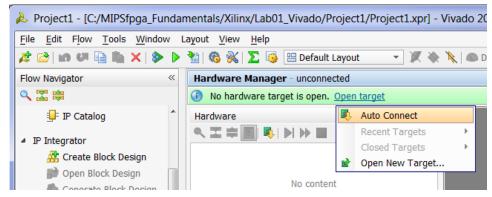

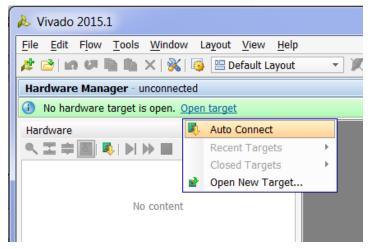

The Hardware Manager window will open. Now click on **Open Target** and choose **Auto Connect**, as shown in Figure 34.

Figure 34. Hardware Manager window, Auto Connect

After you click on *Auto Connect*, Vivado takes several seconds to connect to the target FPGA on the Nexys4 DDR board. You will see the following warning, that you can ignore:

WARNING: [Labtools 27-3123] The debug hub core was not detected at User Scan Chain 1 or 3. ...

If you see the message "No hardware target is open," two causes are most likely:

- You forgot to plug in the Nexys4 DDR board into your computer and/or turn it on.

- You need to install/reinstall the driver for the Nexys4 DDR board's USB programmer cable. Refer to instructions in the MIPSfpga Getting Started Guide if you need help reinstalling the driver.

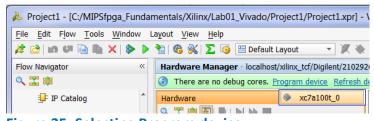

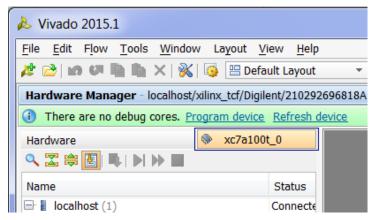

Now click on **Program device** and select **xc7a100t 0**, as shown in Figure 35.

Figure 35. Selecting Program device

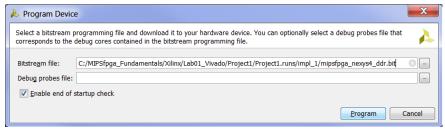

The Program Device window will open, as shown in Figure 36. The Bitstream file box should autopopulate, but if it does not, choose:

MIPSfpga Fundamentals\Xillinx\Lab01 Vivado\Project1\Project1.runs\impl 1\mipsfpga nexys4 ddr.bit

Figure 36. Program device with bitstream file

Leave the **Enable end of startup** box selected and click **Program**.

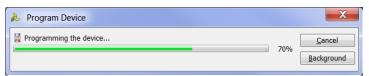

A window will pop up showing the programming progress, as shown in Figure 37. Programming the Artix-7 FPGA on the Nexys4 DDR board will take several seconds. Once it is complete, the progress window will close.

Figure 37. Program Device progress window

The MIPSfpga system is now downloaded onto the Nexys4 DDR board. Push the red reset pushbutton (labeled CPU RESET on the board, see Figure 32) to reset and start the MIPSfpga core. You will now see the LEDs display increasingly incremented values.

The MIPSfpga system is loaded with the IncrementLEDsDelay program. The machine code for this program is in the ram\_rest\_init.txt file located in the same directory as the Verilog files (i.e., in MIPSfpga\_Fundamentals\rtl\_up). The IncrementLEDsDelay program is similar to the IncrementLEDs program that you simulated earlier in this lab, but it adds a delay so that our eyes can detect the results on the LEDs. It would have been tedious to simulate thousands of cycles of delay, so we took the delay out of the program code we used for simulation (see Figure 19). The C, MIPS assembly, and machine code for IncrementLEDsDelay is shown in Figure 38 and Figure 39.

```

// C code

# MIPS assembly code

unsigned int val = 1;

# $9 = val, $8 = memory address 0xbf800000

volatile unsigned int*

addiu $9, $0, 1 # val = 1

$8, 0xbf80 # $8=0xbf800000

ledr ptr;

ledr ptr = 0xbf800000;

while (1) {

L1: sw

$9, 0($8)

\# mem[0xbf800000] = val

*ledr ptr = val;

addiu $9, $9, 1

\# val = val+1

```

```

delay:

val = val + 1;

# loop 2,500,000x

// delay

lui

$5, 0x026 # $5 = 2,500,000

ori

$5, $5, 0x25a0

$6, $0, $0 # $6 = 0

add

L2: sub

$7, $5, $6 # $7 = 2,500,000 - $6

addi $6, $6, 1 # increment $6

bgtz $7, L2

# finished?

# branch delay slot

nop

begz $0, L1

# branch to L1

# branch delay slot

nop

```

Figure 38. IncrementLEDsDelay program

```

24090001 // bfc00000:

addiu $9, $0, 1

3c08bf80 // bfc00004:

lui $8, 0xbf80

ad090000 // bfc00008: L1:

$9, 0($8)

SW

25290001 // bfc0000c:

addiu $9, $9, 1

3c050026 // bfc00010: delay: lui $5, 0x026

34a525a0 // bfc00014:

ori

$5, $5, 0x25a0

00003020 // bfc00018:

add

$6, $0, $0

00a63822 // bfc0001c: L2:

sub

$7, $5, $6

20c60001 // bfc00020:

addi $6, $6, 1

1ceOfffd // bfc00024:

bgtz $7, L2

00000000 // bfc00028:

nop

1000fff6 // bfc0002c:

$0, $0, L1

beq

00000000 // bfc00030:

nop

```

Figure 39. ram\_reset\_init.txt memory initialization file for IncrementLEDsDelay

The next labs will show how to write, compile, download, and run C and MIPS assembly programs on the MIPSfpga system.

# Lab 2 C Programming

These materials produced in association with Imagination.

Join our University community for more resources.

community.imgtec.com/university

# MIPSfpga Lab 2: C Programming

# 3. Introduction

In this lab you will learn to program the MIPSfpga processor in C. You will first complete a tutorial on writing, compiling, and downloading an example C program. Then you will write your own C program to calculate the Fibonacci numbers.

# 4. MIPSfpga C Tutorial

The MIPSfpga processor is programmed using Imagination's Codescape compiler tools. If you have not already, install the Codescape SDK and OpenOCD by running the installer located here:

MIPSfpga Fundamentals\Scripts\OpenOCD-0.9.3-Installer.exe

If you used a version earlier than 1.2 of the MIPSfpga Getting Started Guide, you will need to update the Codescape/OpenOCD installation by running the installer indicated above.

Codescape supports programming in both C and assembly language. You will use C in this lab and MIPS assembly language in Lab 3.

In this tutorial, you will learn to write and compile a simple program that reads the value of the switches on the Nexys4 DDR board and flashes their values to the LEDs. You'll also learn to step through a program and debug it using the Bus Blaster probe and gdb, which is part of the Codescape tools.

# **Example C Program**

Before writing your own program, we walk you through the steps of compiling, debugging, and running a program using some example code. Browse to this directory:

```

MIPSfpga Fundamentals\Xilinx\Lab02 C\ReadSwitches

```

Open the file main.c using a text editor such as Notepad or Wordpad. The main.c file contains the ReadSwitches program, as shown in Figure 40.

```

int main() {

volatile int *IO_SWITCHES = (int*)0xbf800008;

volatile int *IO_LEDR = (int*)0xbf800000;

volatile unsigned int switches;

while (1) {

```

```

switches = *IO_SWITCHES;

*IO_LEDR = switches;

delay();

*IO_LEDR = 0; // turn off LEDs

delay();

}

return 0;

}

void delay() {

volatile unsigned int j;

for (j = 0; j < (1000000); j++); // delay

}</pre>

```

Figure 40. ReadSwitches C program

The following variable declarations make the variables IO\_SWITCHES and IO\_LEDR *point to* the addresses 0xbf800008 and 0xbf800000, which are the memory-mapped I/O addresses of the switches and LEDs, respectively, on the Nexys4 DDR board.

```

volatile int *IO_SWITCHES = (int*)0xbf800008;

volatile int *IO LEDR = (int*)0xbf800000;

```

Memory-mapped I/O was described in the MIPSfpga Getting Started Guide and will be described further in Lab 5. A read to address 0xbf800008 returns the value of the switches in the lower 16 bits (and 0's in the upper 16 bits), and a write to 0xbf800000 displays the lower 16 bits of the value on the LEDs.

The program reads the switches on the FPGA board by reading address 0xbf800008:

```

switches = *IO SWITCHES;

```

The program then writes that value to the LEDs by writing to address 0xbf800000, the memory-mapped address of the LEDs.

```

*IO_LEDR = switches;

```

The program then delays some time, turns the LEDs off, then delays again before repeating.

```

delay();

*IO_LEDR = 0;

delay();

```

The variables switches and j are declared volatile so that they are not optimized away by the compiler.

It is critical to declare variables related to hardware **volatile** so that the compiler does not optimize them away.

# **Compiling, Running, and Debugging**

Now compile, run, and debug the ReadSwitches example C program on the MIPSfpga core using the following steps, described in detail below.

- **Step 1.** Download the MIPSfpga system onto the Nexys4 DDR board

- **Step 2.** Compile the C program

- **Step 3.** Load the C program onto MIPSfpga using Bus Blaster

- Step 4. Debug the C program using gdb as needed

Remember, that to complete these labs you need to have installed all of the required software and drivers (Vivado, Codescape, and OpenOCD, as well as Bus Blaster and Nexsy4 DDR board drivers) as described in the MIPSfpga Getting Started Guide.

# Step 1. Download the MIPSfpga system to the Nexys4 DDR board

Figure 41. Open Vivado's Hardware Manager

Click on **Open Target \(\rightarrow\) Auto Connect** (see Figure 42). **Warning:** Sometimes Vivado crashes at this point. Simply reopen Vivado if that happens.

Figure 42. Autoconnect to FPGA on Nexys4 DDR board

Now click on **Program device**  $\rightarrow$  xc7a100t\_0 (see Figure 43).

Figure 43. Program device

In the Program Device window, select the bitfile you created in Lab 1 (or the one provided at MIPSfpga\_Fundamentals\Xilinx\Lab01\_Vivado\mipsfpga\_nexys4\_ddr.bit). Then click Program. Leave the Debug probes file blank.

Click on the red CPU Reset button on the Nexys4 DDR board to reset the MIPSfpga core and begin running the pre-loaded program that displays incremented values on the LEDs.

## Step 2. Compile the example program

Now compile the ReadSwitches example C program by opening a command shell. To do so, go to the **Start menu**, type in **cmd.exe**, and select cmd.exe. Or you can shift-right-click on an empty space on your screen and select "Open command window here". In the command

shell, change to the MIPSfpa\_Fundamentals\Xilinx\Lab02\_C\ReadSwitches directory. For example, if MIPSfpga\_Fundamentals is in C:\ type:

```

cd C:\MIPSfpga Fundamentals\Xilinx\Lab02 C\ReadSwitches

```

Compile the example C code by typing make at the prompt in the command window:

```

make

```

This runs the Makefile, which compiles the user code (found in main.c) with the boot code (found in boot.S and the other .S files). Open and view the Makefile using a text editor such as Notepad or Wordpad. For future programs, any C program files can be placed under "CSOURCES="

```

CSOURCES= \

main.c

```

Below is a brief description of the main parts of the Makefile. The top part of the file gives the names and locations of the compiler tools (gcc, ld, objdump, etc.). These compiler tools are provided with Codescape. They are GNU tools targeted to the MIPSfpga processor.

```

ifndef MIPS_ELF_ROOT

$(error MIPS_ELF_ROOT must be set to point to toolkit

installation root)

endif

CC=mips-mti-elf-gcc

LD=mips-mti-elf-ld

OD=mips-mti-elf-objdump

OC=mips-mti-elf-objcopy

SZ=mips-mti-elf-size

```

The next part of the Makefile indicates the flags to use for compiling and loading the program.

```

CFLAGS = -01 -g -EL -c -msoft-float -march=m14kc LDFLAGS = -EL -msoft-float -march=m14kc -Wl,-Map=FPGA_Ram_map.txt

```

For the C flags, -01 says to use optimization level 1. You can change this to higher optimization levels as desired, for example optimization level 2 (-02) or 3 (-03). It is typically a good idea to

debug your code using the lowest optimization level (0 or 1). Then, once your code is working, increase the optimization level to produce faster, denser code. <code>-march=m14kc</code> indicates to target the M14K MIPS microAptiv architecture, <code>-msoft-float</code> says that there is no floating-point unit and to use software floating point routines instead.

The LDFLAGS are used when creating the ELF file, which will provide the program code as well as information about how to load the program and data into the MIPSfpga system's memory. Generally, the LDFLAGS indicate to not generate any floating point instructions (-msoftfloat) and to target the M14K MIPS architecture. The file indicated (FPGA\_Ram\_map.txt) describes how and where the program, boot code, and data will be loaded into memory, according to the physical memory map shown in Lab 1. The rest of the LD flags (LDFLAGS += ...) indicate where to place the program, boot code, stack, etc. in memory.

The remainder of the Makefile describes how to compile the program and to clean the directory (i.e., remove files created during compilation). To clean the directory of files created during compilation, type the following at the command prompt:

```

make clean

```

If you just cleaned the directory, compile the program (main.c) again by typing make at the command prompt. Notice that at the end of compilation, the Makefile outputs the size of the executable, as shown in **Error! Reference source not found.**.

```

C:\>cd MIPSfpga_Fundamentals\Xilinx\Lab02_C\ReadSwitches

C:\MIPSfpga_Fundamentals\Xilinx\Lab02_C\ReadSwitches>make

mips-mti-elf-gcc    -EL -msoft-float -march-m14kc -Wl,-Map-FPGA_Ram_map.txt -T uhi

32.ld -Wl,--defsym,__flash_start=0xbfc00000 -Wl,--defsym,__flash_app_start=0x800

00000 -W1,--defsym,__app_start=0x80000000 -W1,--defsym,__stack=0x80040000 -W1,-

defsym,__memory_size=0x1f800 -Wl,-e,0xbfc00000 boot.o main.o -o FPGA Ram.elf

mips-mti-elf-size FPGA_Ram.elf

text

bss

hex filename

data

dec

9132

1204

1072

11408

2c90 FPGA_Ram.elf

mips-mti-elf-objdump -D -S -1 FPGA_Ram.elf > FPGA_Ram_dasm.txt

mips-mti-elf-objdump -D FPGA_Ram.elf > FPGA_Ram_modelsim.txt

mips-mti-elf-objcopy FPGA_Ram.elf -O srec FPGA_Ram.rec

C:\MIPSfpga_Fundamentals\Xilinx\Lab02_C\ReadSwitches>

```

Figure 44. Command shell output of Makefile

The text is **9132** bytes, the data is **1204** bytes and the bss segment (static data that should be initialized to 0) is **1072** bytes for a total of **11408** = **0x2c90** bytes. This fits easily within the MIPSfpga memory space. However, you will want to keep your eye on these numbers for larger programs to make sure they fit within MIPSfpga's physical memory.

You should now see the following files in the ReadSwitches directory:

- FPGA Ram.elf

- FPGA Ram dasm.txt

- FPGA\_Ram\_modelsim.txt

- main.o

**FPGA\_Ram.elf** is the main output of compilation. It is the ELF (executable and linkable format) executable that you will use to load the program into the memory of the MIPSfpga core.

**FPGA\_Ram\_dasm.txt** is a *disassembled* version of the executable. It is basically a human-readable version of the ELF file that shows instruction addresses and instructions interspersed with the line numbers of the higher-level (assembly or C) source code.

**FPGA\_Ram\_modelsim.txt** is another human-readable version of the ELF file, but it is not interspersed with the source code information. It shows the memory addresses and corresponding instructions/data, including those memory addresses that should be initialized to 0. We will use this file to create memory definition files for simulation of compiled programs using Modelsim.

**main.o** is the executable and linkable version of main.c.

Open FPGA\_Ram\_dasm.txt using a text editor to see where the boot code and user code will be placed. The top of the file shows the boot code, starting at 0x9fc00000. Recall that this virtual address maps to physical address 0x1fc000000, which is the physical address of the first instruction fetched upon reset of the MIPSfpga core.

Near the bottom of the file, you can view the user code from main.c, starting at 0x8000075c. This will map to physical addresses starting at 0x0000075c.

## Step 3. Load the C program onto the MIPSfpga system using Bus Blaster

Now that the example program is compiled, you will load it onto the MIPSfpga core using the Bus Blaster probe. First, connect the Bus Blaster probe to the Nexys4 DDR board, as shown in Figure 45. Do so by connecting the two rows of 6 header pins into the small Adapter Board. Then connect the Adapter Board into the PMOD-B port of the Nexys4 DDR board, as shown in the figure. Connect one side of the ribbon cable into the small Adapter board and the other side

into the Bus Blaster probe. Connect one side of the USB cable between the Bus Blaster probe and your computer. Remember, it is best to **use the same port** for the Bus Blaster probe as the one on which you installed the drivers for it.

Probe

**Bus Blaster**

Now open a command shell (i.e., Start menu → cmd.exe.) In the command shell, change to the MIPSfpga\_Fundamentals\Scripts\Nexys4\_DDR directory. For example, if MIPSfpga\_Fundamentals is located on the C drive, type the following at the shell prompt:

Figure 45. Nexys4 DDR board connected to the Bus Blaster probe

cd C:\MIPSfpga Fundamentals\Scripts\Nexys4 DDR

Now you will run the **loadMIPSfpga.bat** script that will (1) compile the program, (2) set up a connection to the MIPSfpga core using OpenOCD, (3) download the program onto the MIPSfpga

system, and (4) allow you to use the Gnu debugger (gdb) to load and debug the program on the MIPSfpga core.

Run the loadMIPSfpga.bat batch script supplying the directory of the ReadSwitches program as the argument. For example, if MIPSfpga\_Fundamentals is on the C drive, at the command font, type:

```

loadMIPSfpga.bat C:\MIPSfpga Fundamentals\Xilinx\Lab02 C\ReadSwitches

```

### Or you could type:

```

loadMIPSfpga.bat ..\..\Xilinx\Lab02_C\ReadSwitches

```

After running the script, you will see the ReadSwitches program running on the MIPSfpga core. Recall that the ReadSwitches program repeatedly reads the value of the switches and flashes that value on the LEDs. Toggle some of the switches at the bottom of the Nexys4 DDR board and watch as the corresponding LEDs flash.

The loadMIPSfpga.bat script first opens a shell to compile the specified program using make. It then opens up two more shells to create the OpenOCD connection and run gdb. After you are finished with a program, you need to close these two windows.

#### Step 4. Debug the C program using gdb as needed

Although this ReadSwitches program works and requires no debugging, we will show you how to go through the process of debugging using gdb, supplied as part of the Codescape SDK.

Click on the gdb command shell that was opened by the loadMIPSfpga.bat script in the previous step. Enter the sequence of commands shown in Table 1 to halt the program, set breakpoints, view variable and register values, etc.

Table 1. gdb command sequence

| Command            | Description                                                              |

|--------------------|--------------------------------------------------------------------------|

| monitor reset halt | Reset and stop the processor. Notice the program stopped running.        |

|                    | Shortcut: mo reset halt                                                  |

| b main             | Set a breakpoint at the main function. (Short for: "break main".)        |

|                    | Notice that the breakpoint is set at 0x800007b4, just after the code for |

|                    | the delay function and stack operations (located at addresses            |

|                    | 0x8000075c – 0x800007b0).                                                |

|                    |                                                                          |

|                    | Note that you can set breakpoints even when the processor is running,    |

|                    | but the breakpoints will take effect only when the processor is halted   |

|                    | (mo reset halt).                                                         |

| b *0x800007b8 | Set a breakpoint at instruction address 0x800007b8. In the                  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------|--|--|--|--|

|               | ReadSwitches C program, this is the load word instruction (1w) that         |  |  |  |  |

|               | reads the value of the switches (see                                        |  |  |  |  |

|               | MIPSfpga_Fundamentals\Xilinx\Lab02_C\ReadSwitches\FPGA_Ram_d                |  |  |  |  |

|               | asm.txt)                                                                    |  |  |  |  |

|               | 800007b8: 8e020008 lw v0,8(s0)                                              |  |  |  |  |

|               | Note that you could also have typed: b 20                                   |  |  |  |  |

|               | This would set a breakpoint at line 20 of main.c                            |  |  |  |  |

| b *0x800007c4 | Set a breakpoint at instruction address 0x800007c4. In the                  |  |  |  |  |

|               | ReadSwitches C program, this is the store word instruction (sw) that        |  |  |  |  |

|               | writes to the LEDs (see                                                     |  |  |  |  |

|               | MIPSfpga_Fundamentals\Xilinx\Lab02_C\ReadSwitches\FPGA_Ram_d                |  |  |  |  |

|               | asm.txt)                                                                    |  |  |  |  |

|               | 800007c4: ae020000 sw v0,0(s0)                                              |  |  |  |  |

| i b           | List the breakpoints. (Short for: "info breakpoint".) At this point it will |  |  |  |  |

|               | list the breakpoint at instruction addresses 0x800007b4 (main),             |  |  |  |  |

|               | 0x800007b8, and 0x800007c4.                                                 |  |  |  |  |

| С             | Continue the processor execution. (Short for: "continue".) It will stop     |  |  |  |  |

|               | at the first breakpoint, in this case, when it gets to main (instruction    |  |  |  |  |

|               | address 0x800007b4).                                                        |  |  |  |  |

| x/3i \$pc     | Prints 3 instructions starting with the current instruction (\$pc is the    |  |  |  |  |

|               | program counter and contains the address of the current instruction).       |  |  |  |  |

|               | 800007b4: lui s0,0xbf80                                                     |  |  |  |  |

|               | 800007b8: lw v0,8(s0)<br>800007bc: sw v0,16(sp)                             |  |  |  |  |

|               | 3w vo, 10(3p)                                                               |  |  |  |  |

| x/3x \$pc     | Prints 3 instructions in hexadecimal, starting at the address specified.    |  |  |  |  |

| С             | Continue to the next break point, which is at 0x800007b8.                   |  |  |  |  |

| stepi         | Executes a single instruction. For example, now you will see the PC         |  |  |  |  |

|               | increment to 0x800007bc.                                                    |  |  |  |  |

|               | Shortcut: si                                                                |  |  |  |  |

| si            | Step one more instruction. (You can also simply press the Enter key to      |  |  |  |  |

|               | repeat the last gdb command.)                                               |  |  |  |  |

| p switches    | Now that the switches have been read, we can print the value of the         |  |  |  |  |

|               | variable switches. (Short for: "print switches".) For example,              |  |  |  |  |

|               | if the 3 least significant switches are 1 (i.e., in the UP position),       |  |  |  |  |

|               | switches will have the value 7.                                             |  |  |  |  |

| p/x switches  | Prints the value of the switches variable in hexadecimal.                   |  |  |  |  |

| p/x &switches | Prints the address of the switches variable                                 |  |  |  |  |

|               |                                                                             |  |  |  |  |

| irv0              | Print the value of register $v0$ only. At this point, $v0$ holds the value of |

|-------------------|-------------------------------------------------------------------------------|

|                   | the FPGA board switches. This value will be written to the LEDs by the        |

|                   | store word (sw) instruction at 0x800007c4.                                    |

| С                 | Continue program execution. (Short for: "continue".) Execution is now         |

|                   | at 0x800007c4, the store word instruction that will write the value of        |

|                   | the switches to the LEDs.                                                     |

| i r s0            | Print the value of register $s0. s0$ currently holds the memory-mapped        |

|                   | I/O address of the LEDs: 0xbf800000.                                          |

| irv0              | Print the value of register $v0. v0$ holds the value of the switches that     |

|                   | will get written to the LEDs.                                                 |

| si                | Execute the store word instruction and watch as the LEDs are updated          |

|                   | to the value of the switches.                                                 |

| d 1               | Delete breakpoint 1 (type i b to list the breakpoints with their              |

|                   | numbers). This deletes the breakpoint at the beginning of main.               |

| monitor reset run | Reset and run the processor. This will run the processor without              |

|                   | breakpoints, even if breakpoints have been set.                               |

|                   |                                                                               |

|                   | Shortcut: mo reset run                                                        |

For a list of other gdb commands, refer to the GDB User Manual available as a link on this webpage:

```

http://www.gnu.org/software/gdb/documentation/

```

## 5. MIPSfpga Exception Handler

MIPSfpga can enter the exception handler for various reasons including accessing an illegal address or attempting to execute an unknown instruction. Here we show how to write an exception handler for MIPSfpga, so that you will know when an exception occurs. Browse to MIPSfpga\_Fundamentals\Xilinx\Lab02\_C\ExceptionHandler and open main.c. View the \_mips\_handle\_exception function, as shown below. This function, which will be called upon an exception, displays 0x8001 on the LEDs to indicate that an exception occurred. You could choose a different value to output. If this function does not exist in your code, upon an exception, the processor simply hangs.

```

void _mips_handle_exception(void* ctx, int reason) {

volatile int *IO_LEDR = (int*)0xbf800000;

*IO_LEDR = 0x8001; // Display 0x8001 on LEDs to indicate error state

while (1);

```

}

To illustrate what happens when an exception occurs, the code in this program intentionally causes an exception by attempting to write to address 0 be executing the code below.

```

volatile int *test_error = (int*)0x0; *test error = 56; // write to address 0 will cause an exception

```

Compile and run this code on the MIPSfpga system. At a command shell prompt, change to the MIPSfpga Fundamentals\Scripts\Nexys4 DDR directory and type:

```

loadMIPSfpga.bat ..\..\Xilinx\Lab02 C\ExceptionHandler

```

You will want to include this exception handler function (\_mips\_handle\_exception) in all of your code to detect when an exception occurs.

#### 6. Fibonacci Numbers

Now you will write your own C program, compile it, and run it on MIPSfpga. Create a program that will calculate and display the first 11 Fibonacci numbers on the LEDs. Each number in the Fibonacci series is the sum of the previous two numbers. Table 2 lists the first few numbers in the series.

**Table 2: Fibonacci Series**

| n      | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8    | 9    | 10   | 11   |  |

|--------|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|--|

| fib(n) | 1   | 1   | 2   | 3   | 5   | 8   | 13  | 21   | 34   | 55   | 89   |  |

| fib(n) | 0x1 | 0x1 | 0x2 | 0x3 | 0x5 | 0x8 | 0xd | 0x15 | 0x22 | 0x37 | 0x59 |  |

We can also define the fib function for negative values of n. To be consistent with the definition of the Fibonacci series, what would the following values be?

These values are useful when writing a loop to compute fib(n) for all non-negative values of n.

Make a copy of the Lab02\_C/ExceptionHandler folder and rename the new folder Fibonacci. Write your program in the main.c file in that folder. Your program should compute the Fibonacci numbers for n = 1...11 and output each Fibonacci number to the LEDs. The LEDs should display the Fibonacci numbers in binary, with a delay between each number so that they are viewable.

Once you have finished writing your program, use the make command to compile it. If there are any errors, fix them and recompile.

After your Fibonacci program compiles without errors, load it onto the MIPSfpga core by:

- 1. Opening a command shell

- 2. Changing to the MIPSfpga Fundamentals\Scripts\Nexys4 DDR directory

- 3. Typing at the command prompt:

```

loadMIPSfpga.bat C:\MIPSfpga Fundamentals\Xilinx\Lab02 C\Fibonacci

```

Table 2 lists the Fibonacci numbers in hexadecimal to help you read the binary values on the LEDs. In later labs, you will expand the MIPSfpga hardware to enable you to use the 7-segment displays available on the Nexys4 DDR FPGA board. But for now, remember that you can also use breakpoints in gdb to examine the values produced by your program.

# Lab 5

Memory-Mapped I/O: 7-Segment Displays

These materials produced in association with Imagination.

Join our University community for more resources.

community.imgtec.com/university

## MIPSfpga Lab 5:

## Memory-Mapped I/O: 7-Segment Displays

#### 7. Introduction

In this lab you will learn about memory-mapped inputs and outputs (I/O) by building hardware modules to expand the capability of the MIPSfpga system so that it can write to the 7-segment displays on the Nexys4 DDR board. You will then test your new hardware by simulating a short sequence of MIPS assembly code. At the end of the lab, you will write C programs that display the value of the switches on the 7-segment displays.

## 8. MIPSfpga Memory-Mapped I/O

A processor uses the memory interface to interact with peripheral devices, such as the switches, LEDs, and 7-segment displays on the Nexys4 DDR FPGA board. *Memory-mapped I/O* enables a processor to write to or read from a peripheral device in the same manner that it reads or writes memory. Each peripheral device is assigned one or more memory addresses. When the processor accesses such a memory address, the peripheral device is accessed instead of memory. The MIPSfpga system uses the AHB-Lite bus to access external memory and peripherals.

#### **AHB-Lite Bus**

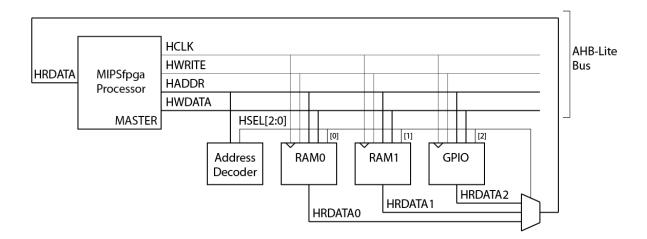

The AHB-Lite bus has a clock, write enable, address, and read and write data signals (HCLK, HWRITE, HADDR, HRDATA, and HWDATA), as shown in Figure 46. The "H" prefix indicates that they are part of the AHB-Lite bus. Memory and peripherals are connected to this interface to receive and supply data. The MIPSfpga core sends these signals to the AHB-Lite Bus:

- HCLK: the 50 MHz system clock

- **HWRITE**: write enable (1 when writing, 0 when reading)

- HADDR: the address being read or written

- HWDATA: the data being written on a write

The MIPSfpga core receives the following input from the AHB-Lite bus:

HRDATA: the read data produced by memory or the peripherals

The MIPSfpga system has three modules on the AHB-Lite bus: two memories (RAMO and RAM1) and a general-purpose I/O module (GPIO). RAMO contains the boot code and RAM1 contains the user code and data. The GPIO unit interfaces with the LEDs, switches, and pushbuttons on the Nexys4 DDR board.

Figure 46. MIPSfpga processor with three peripheral devices

In addition to the three peripherals, the memory-mapped I/O interface requires an Address Decoder and a multiplexer. Depending on the address generated by the processor (HADDR[31:0]), the Address Decoder will enable the processor to access one of the three modules. The Address Decoder generates a select signal HSEL[2:0] that is used by the modules and by the 3:1 multiplexer.

RAMO holds the boot code (virtual addresses 0xbfc00000-0xbfc1fffc = physical addresses 0x1fc00000-0x1fc1fffc). RAM1 holds the user code (virtual addresses 0x80000000-0x8003fffc = physical addresses 0x00000000-0x0003fffc). The LEDs, switches, and pushbuttons on the Nexys4 DDR board are mapped to virtual memory addresses 0xbf800000-0xbf80000c, as shown in Table 3. The processor code uses virtual memory addresses, and the AHB-Lite bus receives physical addresses. The memory management unit (MMU) on the MIPSfpga core performs this address translation.

Table 3. Memory addresses for Nexys4 DDR FPGA board

| Virtual address | Physical address | Signal Name | Nexys4 DDR                |

|-----------------|------------------|-------------|---------------------------|

| 0xbf80 0000     | 0x1f80 0000      | IO_LEDR     | LEDs                      |

| 0xbf80 0008     | 0x1f80 0008      | IO_SW       | switches                  |

| 0xbf80 000c     | 0x1f80 000c      | IO_PB       | U, D, L, R, C pushbuttons |

The following sequence of MIPS assembly instructions writes the value 5 to the LEDs:

```

lui $8, 0xbf80  # $8 = 0xbf800000 (address of LEDs) addi $9, $0, 5  # $9 = 5 sw $9, 0($8)

```

Recall that load-upper-immediate (lui) loads the 16-bit value 0xbf80 into the upper half of \$8 and clears the lower half. Upon execution of the store word instruction (sw), HADDR = 0x1f800000, HWRITE = 1, and HWDATA = 5. The Address Decoder detects that address

0x1f800000 belongs to the general-purpose I/O (GPIO) peripheral and asserts HSEL[2], the select signal associated with that peripheral. The GPIO module detects that HSEL[2] and HWRITE are asserted. Because the GPIO module could potentially write to multiple peripherals, the module uses the address to determine that the LEDs should be written with the value on the HWDATA bus. Specifically, a register whose output is physically connected to the LEDs is updated with the value on HWDATA. That way, the value persists until the LEDs are written again by a later instruction.

Similarly, the following sequence of code reads the value of the switches:

```

lui \$8, 0xbf80  # \$8 = base address of the I/O lw \$9, 8(\$8)  # \$9 = value of the switches

```

Upon execution of the load word instruction (1w), HADDR = 0x1f800008 and HWRITE = 0 (indicating a read). The Address Decoder detects that address 0x1f800008 belongs to the GPIO peripheral and asserts HSEL[2] (and keeps the other select signals HSEL[1] and HSEL[0] low). The GPIO module detects the address corresponding to the switches and selects to send the value of the switches to its read data output, HRDATA2. The select signals HSEL[2:0] control the multiplexer. Because HSEL[2] is asserted, the multiplexer sends HRDATA2 through to HRDATA. The MIPSfpga processor then reads the value on HRDATA, as it would with a typical read from memory, and stores that value in \$9. Thus, after the 1w completes, \$9 contains the value of the switches.

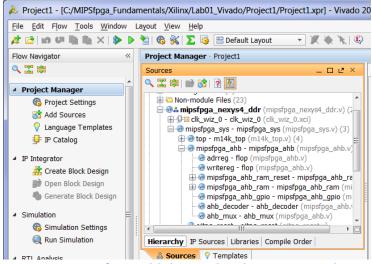

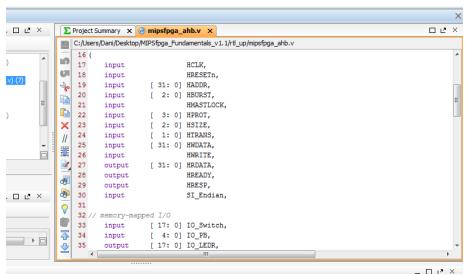

The hardware for the MIPSfpga AHB-Lite modules is located in the mipsfpga\_ahb module and its submodules. It is best to view this module in your Vivado project, so that the hierarchy is clear. Open the Vivado project that you created in Lab 1 (i.e., in MIPSfpga\_Fundamentals\Xilinx\LabO1\_Vivado\Project1). In the Project Manager window, expand mipsfpga\_nexys4\_ddr, then mipsfpga\_sys, then mipsfpga\_ahb to view the mipsfpga\_ahb hierarchy, as shown in Figure 47. Double-click on any of the modules and the Verilog file will open in the neighboring panel.

Figure 47. mipsfpga ahb hierarchy shown in Vivado

For example, double-click on mipsfpga\_ahb to view the interface signals (see Figure 48). Notice all of the AHB-Lite signals from Figure 46 (HCLK, HADDR, HWRITE, HWDATA, and HRDATA). Additional AHB-Lite signals are also available if desired. The module also has the memory-mapped I/O signals IO\_Switch, IO\_PB, and IO\_LEDR that connect to the switches, pushbuttons, and LEDs on the Nexys4 DDR board. IO LEDG is not used on the Nexys4 DDR board.

Figure 48. mipsfpga\_ahb interface signals

The modules instantiated within mipsfpga\_ahb are the three peripherals, address decoder, and multiplexer shown in Figure 46. The corresponding Verilog module names are given in Table 4. View the Verilog code to see how the functionality described above is implemented.

| Tab | le 4. | AHB-L | ite Mod | lu | les |

|-----|-------|-------|---------|----|-----|

|-----|-------|-------|---------|----|-----|

| Name from Figure 46      | Module Name            |

|--------------------------|------------------------|

| RAM0                     | mipsfpga_ahb_ram_reset |

| RAM1                     | mipsfpga_ahb_ram       |

| GPIO                     | mipsfpga_ahb_gpio      |

| Address Decoder          | ahb_decoder            |

| Multiplexer (for HRDATA) | ahb_mux                |

The GPIO module (mipsfpga\_ahb\_gpio) interfaces with the general-purpose I/O on the Nexys4 DDR board. The MIPSfpga system includes access to the LEDs, switches and pushbuttons on the board. In this and the next labs, you will expand the MIPSfpga functionality to extend to other peripherals, starting with the eight 7-segment displays available on the Nexys4 DDR board.

## **7-Segment Displays**

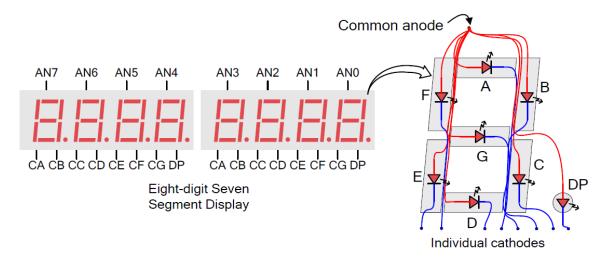

Digits can be represented using 7-segment displays, as shown in Figure 49. Each of the seven segments is labeled a through g. The numbers 0 through F light up the segments shown in Figure 50. For example, the number 0 lights up all but the middle segment, g.

Figure 49. Seven-segment display

Figure 50. Seven-segment display function

Given an input number ranging from 0x0 - 0xF, we will show how to expand the MIPSfpga system to drive the 7-segment displays to show that number. Each segment of the display is low-asserted, so it turns ON when it is 0.

The truth table below (Table 5) shows the inputs (a 4-bit value from 0-15) and outputs for a 7-segment display decoder that takes in a 4-bit number and produces the value of the segments corresponding to that number. So, for example, with an input of "0", the 7-segment display decoder turns all but the middle segment ( $S_g$ ) ON. Thus, the first row for Hexadecimal digit "0" shows all the segments as 0 except  $S_g$ . (Remember that the segments are low-asserted, so they are ON when they receive 0.) The digit "1" should only have  $S_b$  and  $S_c$  ON (so  $S_b$  and  $S_c$  are 0 in that row), and so forth.

Table 5. Truth table for 7-segment display decoder

| Hexadecimal<br>Digit | Inputs         |                |                |                | Outputs |                |                |                |                |                |                |     |

|----------------------|----------------|----------------|----------------|----------------|---------|----------------|----------------|----------------|----------------|----------------|----------------|-----|

| Digit                | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | Sa      | S <sub>b</sub> | S <sub>c</sub> | S <sub>d</sub> | S <sub>e</sub> | S <sub>f</sub> | S <sub>g</sub> | HEX |

| 0                    | 0              | 0              | 0              | 0              | 0       | 0              | 0              | 0              | 0              | 0              | 1              | 01  |

| 1                    | 0              | 0              | 0              | 1              | 1       | 0              | 0              | 1              | 1              | 1              | 1              | 4f  |

| 2                    | 0              | 0              | 1              | 0              | 0       | 0              | 1              | 0              | 0              | 1              | 0              | 12  |

| 3                    | 0              | 0              | 1              | 1              | 0       | 0              | 0              | 0              | 1              | 1              | 0              | 06  |

| 4                    | 0              | 1              | 0              | 0              | 1       | 0              | 0              | 1              | 1              | 0              | 0              | 4c  |

| 5                    | 0              | 1              | 0              | 1              | 0       | 1              | 0              | 0              | 1              | 0              | 0              | 24  |

| 6                    | 0              | 1              | 1              | 0              | 0       | 1              | 0              | 0              | 0              | 0              | 0              | 20  |

| 7                    | 0              | 1              | 1              | 1              | 0       | 0              | 0              | 1              | 1              | 1              | 1              | Of  |

| 8                    | 1              | 0              | 0              | 0              | 0       | 0              | 0              | 0              | 0              | 0              | 0              | 00  |

| 9                    | 1              | 0              | 0              | 1              | 0       | 0              | 0              | 1              | 1              | 0              | 0              | 0c  |

| А                    | 1              | 0              | 1              | 0              | 0       | 0              | 0              | 1              | 0              | 0              | 0              | 08  |

| В                    | 1              | 0              | 1              | 1              | 1       | 1              | 0              | 0              | 0              | 0              | 0              | 60  |

| С                    | 1              | 1              | 0              | 0              | 1       | 1              | 1              | 0              | 0              | 1              | 0              | 72  |

| D                    | 1              | 1              | 0              | 1              | 1       | 0              | 0              | 0              | 0              | 1              | 0              | 42  |

| E                    | 1              | 1              | 1              | 0              | 0       | 1              | 1              | 0              | 0              | 0              | 0              | 30  |

| F                    | 1              | 1              | 1              | 1              | 0       | 1              | 1              | 1              | 0              | 0              | 0              | 38  |

#### **Build 7-segment decoder**

Write a Verilog module that describes the seven-segment display decoder in hardware. The module declaration is provided for you in:

MIPSfpga\_Fundamentals\Xilinx\Lab05\_7seg\VerilogFiles\mipsfpga\_ahb\_sevensegdec.v

The module has a 4-bit input, data[3:0], and a 7-bit output, segments[6:0], corresponding to each of the segments a-g. Test your hardware in simulation using XSIM and debug as needed. In

the next step, you will use this module to drive the 7-segment displays on the Nexys4 DDR board.

## 7-Segment Displays on the Nexys4 DDR board

The Nexys4 DDR board has eight 7-segment digits. All eight of the digits on the Nexys4 DDR board are connected to the same low-asserted segment pins, referred to as CA, CB, CC,...,CG. However, each digit has its own enable which is also low-asserted. Figure 51 shows the eight 7-segment displays on the Nexys4 DDR board. CA is connected to the cathode of the A segment for all eight displays, CB to the cathode of the B segment for all displays, and so forth. Each digit has an enable signal, corresponding to the respective bit of the signal AN[7:0]. AN[7:0] is connected via an inverter, to the anode of all segments for the respective digit. For example, if AN[7] is 0, digit 7 will be driven to the values on CA...CG.

Figure 51. Eight 7-segment displays on the Nexys4 DDR board

(© Nexys4 DDR Reference Manual)

To drive each segment to a different value, the enables (AN[7:0]) and segment values (CA...CG) must be driven sequentially, at a rapid enough speed that our eyes don't detect the flicker. For example, to drive display 0 and 1 to the values 3 and 9, we drive CA...CG to display the value 3, and then drive AN[0] LOW, then we drive CA...CG to display the value 9 and drive AN[1] LOW. If we refresh each digit about every 2 ms, our eyes can't detect any flicker.

#### **Build HDL module to drive Nexys4 DDR 7-segment displays**

Now you will write a Verilog module that drives the eight 7-segment displays on the Nexys4 DDR board. The module declaration is provided in:

MIPSfpga Fundamentals\Xilinx\Lab05 7seg\VerilogFiles\mipsfpga ahb sevensegtimer.v

The module receives the number to display on each of the eight digits (DISP0[3:0] – DISP7[3:0]) and a signal indicating which of the eight displays are enabled (EN[7:0]). It also receives the 50 MHz clock (clk) and a low-asserted reset signal (resetn) as inputs. The outputs are the 7-

segment display enables (DISPENOUT[7:0]) and the values of the 7 segments, A-G (DISPOUT[6:0]). Later in the lab you will connect these outputs through to the top-level module (mipsfpga\_nexys4\_ddr) so that they drive the eight display enables (AN[7:0]) and the seven segment pins (CA...CG).

Your module should drive each enabled digit sequentially about every 2 ms. You will need to use your 7-segment display decoder that you wrote in the previous section. Note that you could expand the functionality of this module to include the decimal point (DP) if desired. Test your hardware in simulation using XSIM and debug as needed.

## Adding Seven-Segment Display Functionality to the GPIO AHB-Lite Module

Now that you have written the hardware modules that will write the eight 7-segment displays, add functionality to the MIPSfpga system to interface with the displays. Your goal is to enable the user to write to the eight 7-segment displays using sw. Start by doing the following:

- 1. Assign memory-mapped I/O addresses to the enable signal and each of the eight digits

- 2. Modify the GPIO module to detect these addresses and store the written data to the associated memory-mapped I/O registers

- 3. Connect these registers to the mipsfpga\_ahb\_sevensegtimer module you just created

To make these changes, you will need to modify the following files (found in the MIPSfpga\_Fundamentals\rtl\_up directory):

- mipsfpga\_ahb\_const.vh

- mipsfpga ahb gpio.v

Below is some guidance for each of the above steps.

#### 1. Assign memory-mapped I/O addresses

Assign nine addresses to the seven-segment displays, one for the enable and eight for the value of each digit, as shown in Table 6. The user will write to these addresses to set the enable and the digit values.

Table 6. Memory addresses for Nexys4 DDR FPGA 7-segment displays

| Virtual address | Physical address | Signal Name  | Nexys4 DDR    |

|-----------------|------------------|--------------|---------------|

| 0xbf80 0010     | 0x1f80 0010      | SEGEN_N[7:0] | AN[7:0]       |

| 0xbf80 0014     | 0x1f80 0014      | SEG0_N[3:0]  | Digit 0 value |

| 0xbf80 0018     | 0x1f80 0018      | SEG1_N[3:0]  | Digit 1 value |

| 0xbf80 001c     | 0x1f80 001c      | SEG2_N[3:0]  | Digit 2 value |

| 0xbf80 0020     | 0x1f80 0020      | SEG3_N[3:0]  | Digit 3 value |

| 0xbf80 0024     | 0x1f80 0024      | SEG4_N[3:0]  | Digit 4 value |

| 0xbf80 0028     | 0x1f80 0028      | SEG5_N[3:0]  | Digit 5 value |

| 0xbf80 002c     | 0x1f80 002c      | SEG6_N[3:0]  | Digit 6 value |

| 0xbf80 0030     | 0x1f80 0030      | SEG7_N[3:0]  | Digit 7 value |

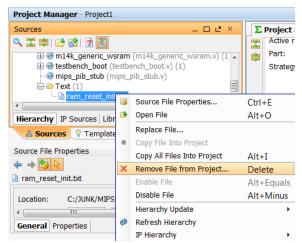

To define these memory-mapped addresses, modify the mipsfpga\_ahb\_const.vh Verilog header file. In Vivado, open Project1. Browse to mipsfpga\_ahb\_const.vh in the Project Manager window (as shown in Figure 52), under Design Sources → Verilog Header.

Figure 52. mipsfpga\_ahb\_const.vh Verilog header file

Define the new memory-mapped I/O addresses for the 7-segment displays as H\_7SEGEN\_ADDR, H\_7SEGO\_ADDR, ... H\_7SEG7\_ADDR. The Address Decoder (ahb\_decoder module) uses the most significant bits of the address to detect which of the three AHB slaves to enable (the reset RAM, program RAM, or GPIO module). Then, once selected, the GPIO module uses the lower bits of the address to determine which of its peripherals should be written or read. Bits 5:2 of the memory-mapped I/O address are saved in another constant: H\_\*\_IONUM, lower in the mipsfpga\_ahb\_const.vh file, as shown below:

```

`define H_LEDR_IONUM (4'h0)

`define H_LEDG_IONUM (4'h1)

`define H_SW_IONUM (4'h2)

`define H_PB_IONUM (4'h3)

```

For example, the switches are mapped to physical address 0x1f800008, so bits 5:2 are 0x2 (i.e., H SW IONUM is 4'h2).

Name the I/O numbers for the 7-segment display variables: H\_7SEGEN\_IONUM, H\_7SEG0\_IONUM, etc. For example since the address for the 7-segment enable is 0x1f800010, H\_7SEGEN\_IONUM is 0x4.

#### 2. Modify the GPIO module

Now modify the GPIO module to detect the nine memory-mapped I/O addresses you just defined and write the data (HWDATA) to those registers when the corresponding address is detected. In Project1 in Vivado, open **mipsfpga\_ahb\_gpio.v.** In the module declaration, declare

and output the enable and segment signals (A-G). Name these signals IO\_7SEGEN\_N[7:0] and IO\_7SEG\_N[6:0], respectively. In a higher-level module, these will drive the enables (AN[7:0]) and segment values (CG...CA) on the Nexys4 DDR board.

You must now create 9 registered values that hold the value of the enables and the values to display on the eight 7-segment display digits. The user will write to these registers using memory-mapped I/O. Name the registered signal that holds the enables SEGEN\_N[7:0]. Name the registers that each hold the 4-bit values to display on the eight digit SEGO\_N[3:0], ...,SEG7\_N[3:0]. Modify the GPIO module so that these registers get written when the correct address is detected.

### 3. Connect these registers to the mipsfpga\_ahb\_sevensegtimer module you just created

Now, within the GPIO module, instantiate and connect the mipsfpga\_ahb\_sevensegtimer module that you built earlier in this lab. You will connect its inputs to the memory-mapped I/O registers (as well as the clock and reset signals) and its outputs to the 7-segment display signals (IO\_7SEGEN\_N and IO\_7SEG\_N).

## Connect the 7-Segment Display Signals to the Nexys4 DDR Board