Что делать, когда выпускник топ-10 мирового вуза не может спроектировать блок сложения A+B

У меня был в свое время практикант из Стенфорда, от которого я получил инсайдерскую информацию, чему их там учат. Потом я интервьировал много студентов, и понял, что если человек не делает самостоятельных проектов в вузе, а просто плывет по течению программы как медуза, то будучи выброшенным на берег индустрии, он становится совершенно беспомощным.

Когда я вижу у недавнего выпускника в резюме какой-то из протоколов в котором используется valid/ready, например AXI или AHB, я прошу его спроектировать блок, у которого на входе два числа A и B, а на выходе их сумма. Разумеется не просто написать SUM=A+B, а еще и поставить valid/ready сигналы на каждый из A, B, SUM, чтобы A и B могли приходить в разное время, а также чтобы блок ждал, если SUM не может быть передана другому блоку сразу.

Некоторые не справляются. Грустно смотреть на человека, который потратил 6 лет своей жизни (4 года в бакалавриате и 2 года в магистратуре) и океан денег на образование — и не может сложить два числа и бьется как угорь на сковородке. То блок не работает когда числа приходят в разное время, то создатель забывает снять valid, и блок на 2+2 выдает не 4, а 4-4-4-4-4-4-4… То числа складываются не попарно, а просто записываются в регистры и на выход идет их текущая сумма, хотя количество аргументов A и B не совпадает. То не отрабатывается backpressure и результаты теряются, то (после того как кандидат написал страницу кода на верилоге) блок работает на половинной производительности, то есть не может принимать поток чисел подряд, а ожидает между ними пропуски (gaps). Короче ведет себя как ChatGPT.

Конечно, если студент сам во время учебы делает скажем правильные open-source проекты, то он вписывается в индустрию легче. Но все равно компании тратят много усилий на переподготовку недавних студентов. Некоторые электронные компании нанимают профессиональных тренеров типа Клифа Каммингса, которые берут три тысячи долларов за неделю трейнинга за_каждого_студента.

Я в свое время пытался привезти Клиффа в Россию, но в первую попытку звезды не сошлись (хотя все топ российские электронные компании согласились прислать по одному-два инженера). А во второй раз настала международная напряженность и все накрылось — Клифф продал свою компанию бОльшей трейнинг-компании и там менеджер не захотел.

Я это все к чему — я на днях прочитал на Хабре что Ядро/Syntacore решили сделать целый внутренний курс для тренировки ASIC проектировщиков из бывших FPGA проектировщиков:

Это в принципе крутая идея, так как отличия front-end ASIC от FPGA инженеров не такие уж большие:

- FPGA инженер с опытом мою задачку про A+B решит.

- В FPGA как правило менее навороченные микроархитектуры, чем в ASIC, но это дело количественное, а не качественное в смысле опыта.

- В ASIC есть больше всякого self-теста, scan chains, энергопотребления — но это в основном забота physical design teams, а не front-end designers.

Замечу что Элон Маск в свой SpaceX сейчас интервьирует на смешанную ASIC/FPGA позицию:

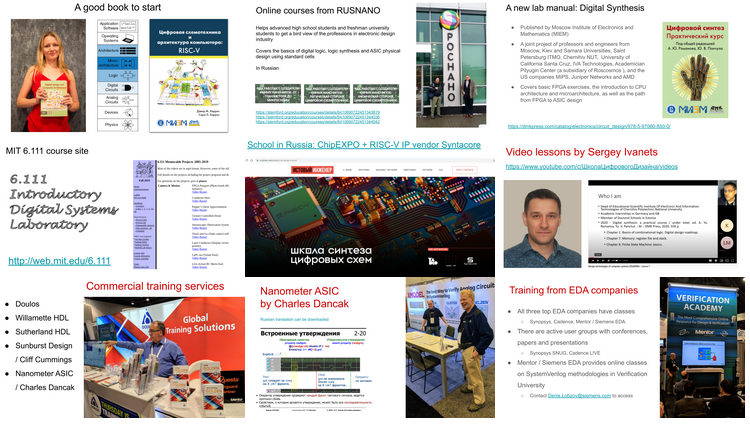

Но что делать тем, кто еще не готов идти в Ядро/Syntacore и хочет натренировать себя в FPGA? Предположим, что у вас есть некий начальный опыт, например почерпнутый из источников, которые я перечислил в презентации для проектов в Средней Азии, курса в ВШЭ МИЭМ или скажем по ссылкам из телеграм-каналов fpgasystems , tinyurl.com/yy79xfer, DigitalDesignSchool , сайта ранних энтузиастов FPGA в России marsohod.org итд:

Следующий шаг — набрать опыта на открытых проектах, и у меня как раз есть такой проект, для которого я собираю команду. Это проект YRV-Plus, см. поддерево Plus в репозитории github.com/yuri-panchul/yrv-plus . Суть проекта — накрутить опций вокруг RISC-V ядра микроконтроллерного класса под названием YRV. В том числе:

- Запустить ядро YRV на дюжине FPGA плат от Altera / IntelFPGA, Gowin, Xilinx, Lattice.

- Сделать скрипты для работы YRV на различных симуляторах: Synopsys VCS, Cadence Xcelium, Siemens EDA / Mentor Questa, Icarus Verilog, Verilator.

- Сделать пару десятков интересных софтверных примеров на ассемблере, в частности с обработкой прерываний.

- Сделать различные варианты linker script для компиляции софтверных примеров на Си.

- Сделать пример разделения общей памяти между тремя такими ядрами. Сделать разделяемую память многобанковой и показать, как количество банков влияет на производительность.

- Сделать пример обмена сообщениями между несколькими ядрами с помощью так называемого gated storage. Одно ядро пишет, а другое читает из адреса, который отображается не на обычную память, а на очередь FIFO. Когда FIFO наполнено, записывающее ядро останавливается на следущей записи. Когда FIFO пустое, читающее ядро останавливается на следующем чтении.Показать изменение производительности в зависимости от глубины FIFO и поведения программ.

- Сделать контроллер SDRAM памяти для разных плат и интегрировать его с YRV.

- Присоединить к ядру различные кэши: полностью ассоциативные, прямого отображения, многосекционные, с различными стратегиями замещения. Показать изменение производительности с различными сценариями доступа к данным.

- Спортировать на YRV какой-нибудь бесплатный RTOS, например FreeRTOS.

- Реализовать в ядре FPU и сравнить его производительность по сравнению с библиотечно-целочисленной реализацией плавающей арифметики (начать со сложения или умножения). Сравнить размер и максимальную тактовую частоту получившихся ядер.

- Реализовать в ядре векторые расширения и продемонстрировать, какое они дают увеличение производительности.

- Присоединить к ядру сопроцессор для работы с графикой, чтобы с ним можно было сделать учебную игровую приставку.

- Измерить производительность ядра YRV на бенчмарках Dhrystone и CoreMark, сравнить с другими открытыми ядрами, в частности: Syntacore SCR1, ядро mirisc от Московского института электронной техники и SweRV EH1 от Western Digital.

- Верифицировать ядро с различными наборами тестов.

- Синтезировать YRV для ASIC с помощью открытого маршрута Open Lane и System-on-Chip (SoC) платформы Caravel. Вот тут-то вы можете начать переучиваться на ASIC.

В частности нужно спортировать YRV на плату Tang Primer 20K c китайским GoWwin FPGA, с которой на фотографии слева работает мой приятель Александр Белиц, инженер из компании Marwell. Эта плата недорогая и вместительная, использует систему разработки от GoWin, которая является альтернативой Intel FPGA Quartus и Xilinx Vivado.

Также в частности стоит спортировать YRV на плату Digilent Nexys4 DDR, которую держит в руках девушка Ирина из Новосибирского Академгородка. Эту плату с системой разработки Xilinx Vivado используют большое количество вузов.

Почему именно процессорное ядро YRV, хотя вокруг этих RISC-V ядер немерянное количество? По комбинации факторов:

- YRV одновременно является полнофункциональным RISC-V ядром (не учебным подможеством), и при этом имеет очень компактный размер, то есть влазит в недорогие FPGA платы.

- YRV написал проектировщик Монте Далримпл, который занимается процессорами с 1970-х годов в компании Zilog, использует Verilog с начала 1990-х годов, спроектировал кучу чипов, в том числе для космоса. То есть это в чистом виде «старый конь борозды не испортит» — Монте чувствует тайминг, пишет все аккуратно и читабельно, понимает какая нужна периферия и контроллер прерываний для микроконтроллера.

- Монте все задокументировал в собственной книжке, которая также описывает весь материал по архитектуре RISC-V необходимый для работы с его процессорным ядром:

К нашей open-source команде, помимо Монте, меня и Белица, присоединился Дмитрий Петренко. Дмитрий одолжил несколько альтеровских плат от программы одалживания FPGA плат Михаила Коробкова и перенес на них YRV. Также Дмитрий написал линкер-скрипт и смог построить маршрут писания программ для YRV на Си (hello world). Вот платы Дмитрия в работе:

Мы недавно с Александром Белицем обедали с Монте Делримплом в Ливерморе, городе, который был недавно в новостях по поводу термояда. Монте там живет. В центре города стоит скульптура — вращающийся шар с фонтаном и надписями про российcко-американское сотрудничество в физике. Кстати по странам происхождения четыре участника проекта являются выходцами из четырех стран — России, Украины, Белоруссии и США — угадайте кто откуда.

Так что присоединяйтесь пятым и более. Репозиторию можете форкнуть у меня или у Дмитрия (ссылка выше). Мы проводим еженедельные созвоны в 9 утра в воскресенье по Калифорнии (это 20.00 вечера воскресенье по Москве).

Но если вы уже изучили простые процессоры и основы FPGA, присоединяйтесь сразу к Ядру/Syntacore . Если нет — можете еще пройти курс лабораторных от МИЭТ по проектированию однотактного процессора с прерываниями и периферией (видео их лекций). И потом присоединиться к новому проекту MIRISC в МИЭТ с более сложным конвейером. Это ситуация «пусть цветут все цветы, заимствуют и меряются друг с другом»